# A.O. Partie 3 – circuits logiques

<http://www.phmartin.info/cours/ao/> (→ TDs, QCMs, corrigés, ...)

Plan (+ 0. Définitions, 3. "TD (partie) 3", "Corrigés QCMs 1+2 et TD 2")

## 1. Circuits combinatoires

### 1.1. Fonctions à 1 ou 2 variables

### 1.2. Fonctions à 2 variables

### 1.3. Axiomes et théorèmes fondamentaux de l'algèbre de Boole

### 1.4. L'opérateur XOR (OU exclusif)

### 1.5. Les opérateurs complets: le NAND et le NOR

### 1.6. Synthèse d'un circuit combinatoire

### 1.7. Analyse d'un circuit combinatoire

### 1.8. Démultiplexeur et multiplexeur

### 1.9. Codeur, décodeur, transcodeur

## 2. Circuits séquentiels (*non sujet à évaluation à partir de 2014-2015*)

### 2.1. Définitions

### 2.2. Exemple d'automate fini

### 2.3. Bistables et bascules: types (D, SR, T, JK) et utilisations

### 2.4. Synthèse d'un circuit séquentiel

### 2.5. Analyse d'un circuit séquentiel

# 0. Définitions

**Fonction logique:** fonction utilisant des variables logiques, i.e., des variables pouvant prendre 2 valeurs (0 ou 1, faux ou vrai, ...).

**Fonction logique incomplètement définie:** quand sa valeur de sortie est indifférente ou non spécifiée pour certaines combinaisons des variables d'entrées; on utilise alors X au lieu de 0 ou 1.

**Circuit logique:** circuit (électronique, [optique](#), [fluidique](#) ([pneumatique](#) [1,2,3,4] / ...) / ...) composé de portes logiques (e.g., porte ET, OU, ...) et réalisant une ou plusieurs fonctions logiques; deux types: circuit combinatoire et circuit séquentiel.

QW "ao3wooclap" sur [la page Moodle du cours](#) :

**Une fonction logique incomplètement définie est ...**

- A) une fonction qui peut être implémentée par différents circuits logiques non équivalents

- B) une fonction dont la valeur de sortie est indifférente ou non spécifiée pour certaines combinaisons des variables d'entrées

- C) une fonction dont la valeur de sortie peut être une variable (au lieu de 0 ou 1) pour certaines combinaisons des variables d'entrées

- D) les 3 dernières réponses sont justes

- E) aucune des 4 dernières réponses n'est juste

# 0. Définitions

**Circuit combinatoire:** circuit où le temps de propagation des signaux n'est pas pris en compte   -> les signaux de sortie ne dépendent que des signaux d'entrée

-> étude via l'algèbre de Boole.

**Circuit séquentiel:** circuit où le temps de propagation des signaux et la mémoire du circuit sont pris en compte

-> les signaux de sortie dépendent de signaux d'entrée précédents (-> notions d'états, de mémoire et de temps) et donc de rétroactions (retours des sorties dans les entrées)

-> étude via la théorie des automates finis.

**Fonction logique d'un circuit combinatoire:** peut se représenter via un diagramme (logigramme), une expression algébrique, ou une table de vérité.

**Table de vérité:** tableau de correspondance entre les états d'entrée et les états de sortie;

s'il y a  $V$  variables en entrées, comme chacune des variables peut prendre 2 valeurs (0 ou 1), il y a  $N=2^V$  combinaisons (et donc lignes dans la table), et une table de vérité à  $N$  variables peut représenter  $2^N$  fonctions;

exemples dans les pages suivantes.

**QW "ao3wooclap" sur la page Moodle du cours :**

**Un circuit séquentiel est ...**

- A) un circuit où le temps de propagation des signaux et la mémoire du circuit sont pris en compte

- B) un circuit dont les sorties peuvent aussi être ses entrées

- C) un circuit qui s'étudie via la théorie des automates finis

- D) les 3 dernières réponses sont justes

- E) aucune des 4 dernières réponses n'est juste

## 1.1. Circuits combinatoires - fonctions à 1 ou 2 variables

Il y a 4 (=  $2^{(2 \text{ puissance } 1)}$ ) fonctions à **1** variable:

identité, NON [NOT] (complémentation, inversion), constante 1 (renvoie toujours 1), constante nulle.

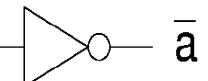

Symboles pour le NON (ici, sur une variable "a"):  $\bar{a}$ ,  $\neg a$ ,  $!a$ ,  $a \rightarrowtail \bar{a}$

Table de vérité pour le NON:

$a \mid \bar{a}$

---+---

0 | 1

1 | 0

---

Il y a 16 (=  $2^{(2 \text{ puissance } 2)}$ ) fonctions à **2** variables (cf. liste page suivante).

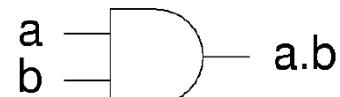

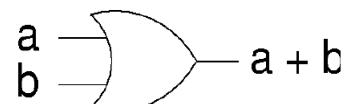

Exemples: le ET et le OU

**ET [AND].** Symboles:  $a \cdot b$ ,  $a \wedge b$ ,  $a b$ ,

**OU [OR].** Symboles:  $a + b$ ,  $a \vee b$ ,

Table de vérité du ET et du OU:

$a \ b \mid a.b \ a+b$

---+-----

0 0 | 0 0

0 1 | 0 1

1 0 | 0 1

1 1 | 1 1

## 1.2. Circuits combinatoires - fonctions à 2 var.

Il y 16 (=  $2^{(2 \text{ puissance } 2)}$ ) fonctions à **2** variables:

| 00 | 01 | 10 | 11 |  | ab                                           |                   |

|----|----|----|----|--|----------------------------------------------|-------------------|

| 0  | 0  | 0  | 0  |  | $F_0 = 0$                                    | (constante nulle) |

| 0  | 0  | 0  | 1  |  | $F_1 = ab$                                   | (fonction ET)     |

| 0  | 0  | 1  | 0  |  | $F_2 = a\bar{b}$                             |                   |

| 0  | 0  | 1  | 1  |  | $F_3 = \bar{a}$                              |                   |

| 0  | 1  | 0  | 0  |  | $F_4 = \bar{a}b$                             |                   |

| 0  | 1  | 0  | 1  |  | $F_5 = b$                                    |                   |

| 0  | 1  | 1  | 0  |  | $F_6 = a \oplus b$                           | (fonction XOR)    |

| 0  | 1  | 1  | 1  |  | $F_7 = a + b$                                | (fonction OU)     |

| 1  | 0  | 0  | 0  |  | $F_8 = \overline{a + b} = \bar{a} \bar{b}$   | (fonction NOR)    |

| 1  | 0  | 0  | 1  |  | $F_9 = \bar{a} \oplus b$                     |                   |

| 1  | 0  | 1  | 0  |  | $F_{10} = \bar{b}$                           |                   |

| 1  | 0  | 1  | 1  |  | $F_{11} = \bar{a} + \bar{b}$                 |                   |

| 1  | 1  | 0  | 0  |  | $F_{12} = \bar{a}$                           |                   |

| 1  | 1  | 0  | 1  |  | $F_{13} = \bar{a} + b$                       |                   |

| 1  | 1  | 1  | 0  |  | $F_{14} = \overline{ab} = \bar{a} + \bar{b}$ | (fonction NAND)   |

| 1  | 1  | 1  | 1  |  | $F_{15} = 1$                                 | (constante 1)     |

QW "ao3wooclap" sur la page Moodle du cours :

Combien de fonctions logiques peuvent être représentées avec des tables de vérité à V variables d'entrée ?

- A)  $2^*V$  fonctions

- B)  $2^V$  fonctions

- C)  $2^N$  fonctions, avec  $N = 2^V$

- D) les 3 dernières réponses sont justes

- E) aucune des 4 dernières réponses n'est juste

# 1.3. Axiomes et théorèmes fondamentaux de l'algèbre de Boole

**Opérateurs de cet algèbre** (par ordre décroissant de priorité):

NON, ET, OU; ils sont suffisants pour synthétiser toute fonction logique.

*Axiomes:*

**Commutativité:**  $a+b = b+a$ ,  $a.b = b.a$

**Distributivité:**  $a.(b+c) = (a.b)+(a.c)$ ,  $a+(b.c) = (a+b).(a+c)$

**Associativité:**  $a+(b+c) = (a+b)+c = a+b+c$ ,  $a.(b.c) = (a.b).c = a.b.c$

**Complémentation/Complémentarité:**  $a+\bar{a} = 1$ ,  $a.\bar{a} = 0$

*Théorèmes:*

**Théorème des constantes:**  $a+0 = a$ ,  $a.0 = 0$ ,  $a+1 = 1$ ,  $a.1 = a$

**Idempotence:**  $a+a = a$ ,  $a.a = a$

**Théorèmes de De Morgan:** non  $(a+b) = \bar{a} \cdot \bar{b}$       non  $(a.b) = \bar{a} + \bar{b}$

**Autres relations:** non  $(\bar{a}) =$  non (non  $a$ ) =  $a$ ,  $a.(a+b) = a$ ,  $(a+b).(a+\bar{b}) = a$

**QW "ao3wooclap". L'expression  $a+(a.b)=a$  est vraie ...**

- A) seulement quand  $a$  est vrai

- B) par exemple quand  $a$  est vrai

- C) toujours

- D) par exemple quand  $a + (\bar{a} \cdot b) = a + b$

- E) les 3 dernières réponses sont justes

**QW "ao3wooclap". L'expression "a.(a+b)" est équivalente à ...**

- A) l'expression " $a + (a.b)$ "

- B) l'expression " $a+a$ "

- C) l'expression " $(a + \bar{b}) \cdot (a + b)$ "

- D) les 3 dernières réponses

- E) aucune des 4 dernières réponses

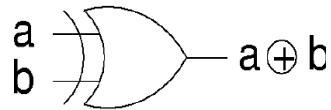

## 1.4. L'opérateur XOR (OU exclusif)

OU exclusif [eXclusive OR (XOR)].

Symboles:  $a \text{ xor } b$ ,  $a \oplus b$

Table de vérité et propriétés du XOR:

| a | b | a xor b |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

|                                                                                                                          |                                                          |

|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| $a \oplus b = \overline{ab} + \overline{a} \overline{b}$                                                                 | $\overline{a \oplus b} = ab + \overline{a} \overline{b}$ |

| $a \oplus 0 = a$                                                                                                         | $a \oplus a = 0$                                         |

| $a \oplus 1 = \overline{a}$                                                                                              | $a \oplus \overline{a} = 1$                              |

| $a \oplus b = b \oplus a$                                                                                                | $(a \oplus b) \oplus c = a \oplus (b \oplus c)$          |

| $a \oplus b = \overline{\overline{a} \overline{b} + ab} = (a + b) (\overline{a} + \overline{b}) = (a + b) \overline{ab}$ |                                                          |

Exemple de question d'évaluation:

**La table de vérité suivante est celle du ... ?**

- A) XOR

- B) NAND

- C) NOR

- D) OR

- E) aucune des 4 dernières réponses n'est juste

| a | b | f(a,b) |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 0      |

| 1 | 1 | 0      |

QWs "ao3wooclap".

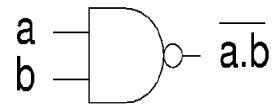

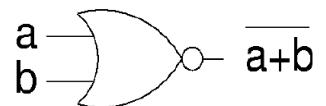

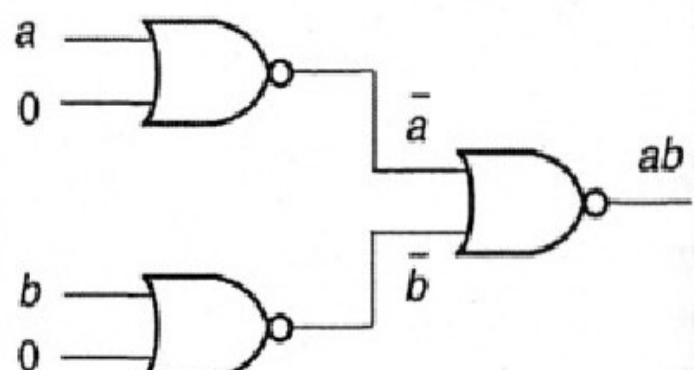

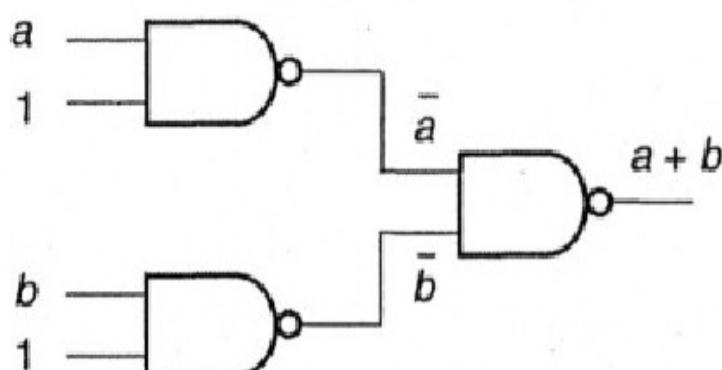

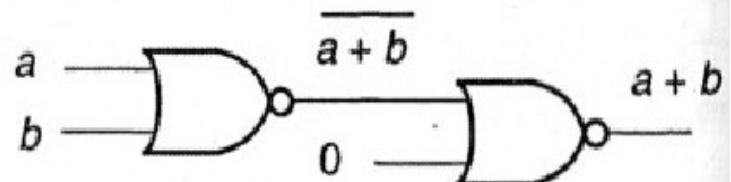

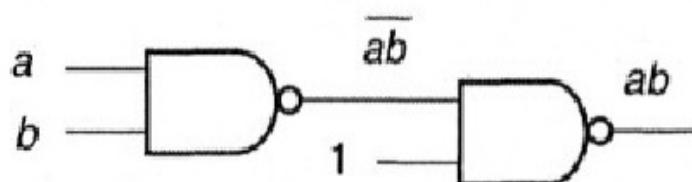

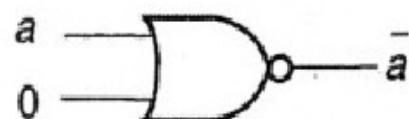

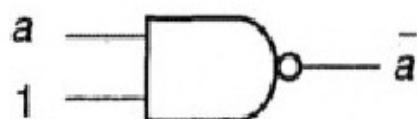

## 1.5. Les opérateurs complets: le NAND et le NOR

**NON ET [NAND].** Symboles:  $a \text{ nand } b$ ,  $\overline{a \cdot b}$ ,

**NON OU [NOR].** Symboles:  $a \text{ nor } b$ ,  $\overline{a + b}$ ,

Toutes les fonctions logiques peuvent être exprimées avec NAND ou NOR, et cela est souvent intéressant économiquement et pour les performances.

Exemples:

Note: ET, OU, NAND et NOR peuvent en fait avoir plus de deux entrées mais pas XOR

## 1.6. Synthèse d'un circuit combinatoire

**Synthèse d'un circuit combinatoire:** déterminer un logigramme à partir de la définition d'une fonction logique ->

1. construire (sa table de vérité et en dériver) une expression algébrique

2. la simplifier, e.g., via les théorèmes de l'algèbre de Boole ou les tables de Karnaugh

3. réaliser la fonction logique à l'aide d'opérateurs (NAND, NOR, ...).

**Forme normale (alias "canonique")** d'une expression:

minterm ou maxterm.

**Minterm:** produit logique ou somme de produits logiques (alias, disjonction de conjonctions), e.g.,  $a \text{ xor } b = \bar{a} \cdot b + a \cdot \bar{b}$

**Maxterm:** somme logique ou produit de sommes logiques (alias, conjonction de disjonctions), e.g.,  $a \text{ xor } b = (a + b) \cdot (\bar{a} + \bar{b})$

**Tables de Karnaugh:** méthode visuelle pour simplifier des fonctions logiques, en particulier avec moins de 6 variables;

exemples dans les pages suivantes.

Exemple de question d'évaluation: **Qu'est-ce qu'un "maxterm" ?**

- A) une somme de produits logiques

- B) quelque chose que l'expression suivante illustre:  $\bar{a} \cdot b + a \cdot \bar{b}$

- C) une fonction prenant le maximum des termes d'une expression

- D) les 3 dernières réponses sont justes

- E) aucune des 4 dernières réponses n'est juste

## 1.6.1. Exemples de table de Karnaugh à 2 ou 3 variables

Soit la fonction  $Z = \bar{a}.b + a.\bar{b} + a.b$

Table de Karnaugh à 2 variables:

Table de vérité

| a | b | Z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

|   |   | a |   |

|---|---|---|---|

|   |   | 0 | 1 |

| b | 0 | 1 | 1 |

|   | 1 | 1 | 1 |

Toutes les cases relatives aux valeurs à 1 de a et b sont encerclées, donc  $Z = a + b$  ( $Z$  est vrai si a ou b est vrai).

De fait,  $Z = \bar{a}.b + a.\bar{b} + a.b + a.b = a.(b+\bar{b}) + b.(a+\bar{a}) = a + b$

Soit la fonction  $Z = \bar{a}.\bar{b}.\bar{c} + a.\bar{b}.c + a.\bar{b}.\bar{c} + a.b.c$

Table de Karnaugh à 3 variables:

|    |  | c  |   |    |  |    |   |

|----|--|----|---|----|--|----|---|

|    |  | a  |   |    |  |    |   |

| ac |  | 00 |   | 01 |  | 11 |   |

|    |  | 0  | 1 |    |  | 1  | 1 |

| b  |  | 0  |   |    |  | 1  |   |

|    |  | 1  |   |    |  |    |   |

$$\rightarrow Z = a.c + \bar{b}.\bar{c}$$

## 1.6.3. Tables de Karnaugh avec 4 variables

$$Z = \overline{a} \cdot \overline{b} \cdot \overline{c} \cdot \overline{d} + \overline{a} \cdot \overline{b} \cdot \overline{c} \cdot d + \overline{a} \cdot \overline{b} \cdot c \cdot d + \overline{a} \cdot b \cdot \overline{c} \cdot d + a \cdot b \cdot \overline{c} \cdot d + a \cdot \overline{b} \cdot \overline{c} \cdot d + a \cdot \overline{b} \cdot \overline{c} \cdot \overline{d} + \overline{a} \cdot b \cdot c \cdot d + a \cdot b \cdot c \cdot d + a \cdot \overline{b} \cdot c \cdot d + \overline{a} \cdot b \cdot c \cdot \overline{d}$$

Table de Karnaugh:

|          |    | <i>b</i> |    | <i>a</i> |    | <i>cd</i> |

|----------|----|----------|----|----------|----|-----------|

|          |    | 00       | 01 | 11       | 10 |           |

| <i>d</i> | 00 | 1        |    |          | 1  |           |

|          | 01 | 1        | 1  | 1        | 1  |           |

| <i>c</i> | 11 | 1        | 1  | 1        | 1  |           |

|          | 10 |          | 1  |          |    |           |

$$\rightarrow Z = d + \overline{b} \cdot \overline{c} + \overline{a} \cdot b \cdot c$$

$$Z = \overline{a} \cdot \overline{b} \cdot \overline{c} \cdot \overline{d} + a \cdot \overline{b} \cdot \overline{c} \cdot \overline{d} + \overline{a} \cdot \overline{b} \cdot c \cdot \overline{d} + a \cdot \overline{b} \cdot c \cdot \overline{d}$$

Table de Karnaugh:

|          |    | <i>b</i> |    | <i>a</i> |    | <i>cd</i> |

|----------|----|----------|----|----------|----|-----------|

|          |    | 00       | 01 | 11       | 10 |           |

| <i>d</i> | 00 | 1        |    |          | 1  |           |

|          | 01 |          |    |          |    |           |

| <i>c</i> | 11 |          |    |          |    |           |

|          | 10 | 1        |    |          | 1  |           |

$$\rightarrow Z = \overline{b} \cdot \overline{d}$$

## 1.6.5. Méthode générale de simplification pour 4 variables

1. encercler les cases à 1 pouvant former des groupes de 8 cases

2. encercler les cases à 1 pouvant former des groupes de 4 cases mais pas de 8 cases

3. encercler les cases à 1 pouvant former des groupes de 2 cases mais pas de 4 cases

4. encercler les cases à 1 qui ne sont pas adjacentes à d'autres 1 et qui ne peuvent former des blocs de 2 cases.

Pour simplifier encore plus à l'aide de portes XOR, NAND et NOR, il faut effectuer des manipulations algébriques.

Pour plus de 4 variables, il faut créer plusieurs tables de Karnaugh.

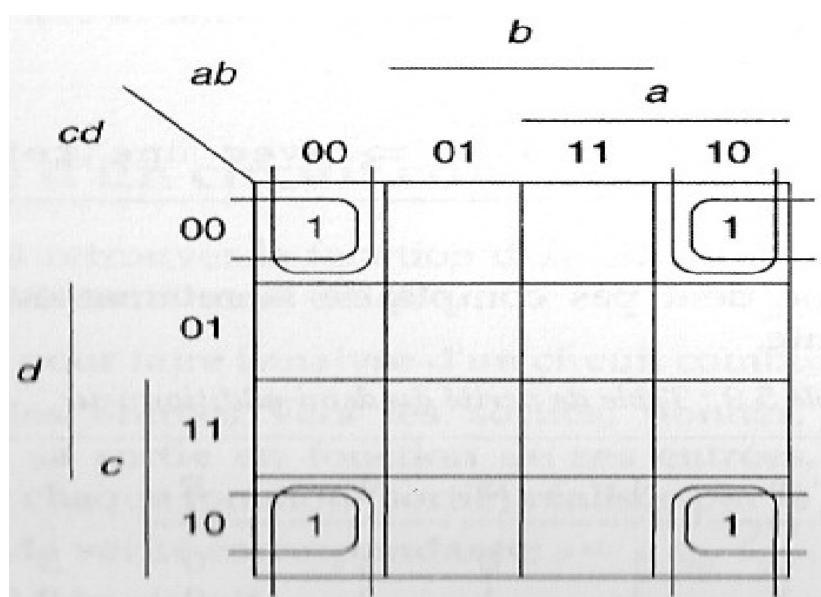

Exemple de question d'évaluation:

**Quelle formule algébrique illustre cette table de**

**Karnaugh ?**

- A)  $Z = a + \bar{b}$

- B)  $Z = \bar{b} + \bar{d}$

- C)  $Z = \bar{a} \cdot \bar{d}$

- D)  $Z = \bar{b} \cdot \bar{d}$

- E) aucune des 4 réponses ci-dessus n'est juste

|  |  | b  |    |    |    |

|--|--|----|----|----|----|

|  |  | ab |    | a  |    |

|  |  | 00 | 01 | 11 | 10 |

|  |  | 1  |    |    | 1  |

|  |  |    |    |    |    |

|  |  |    |    |    |    |

|  |  |    |    |    |    |

cd

d

c

QW "ao3wooclap".

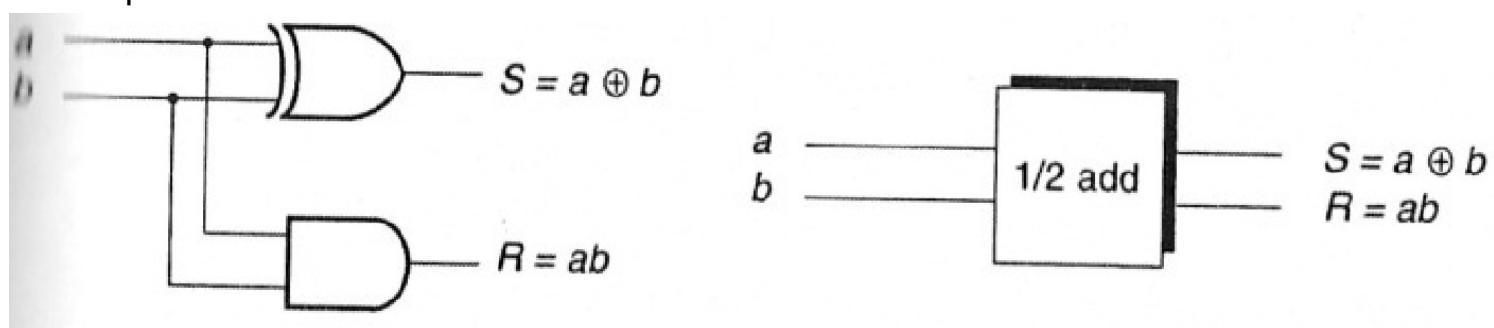

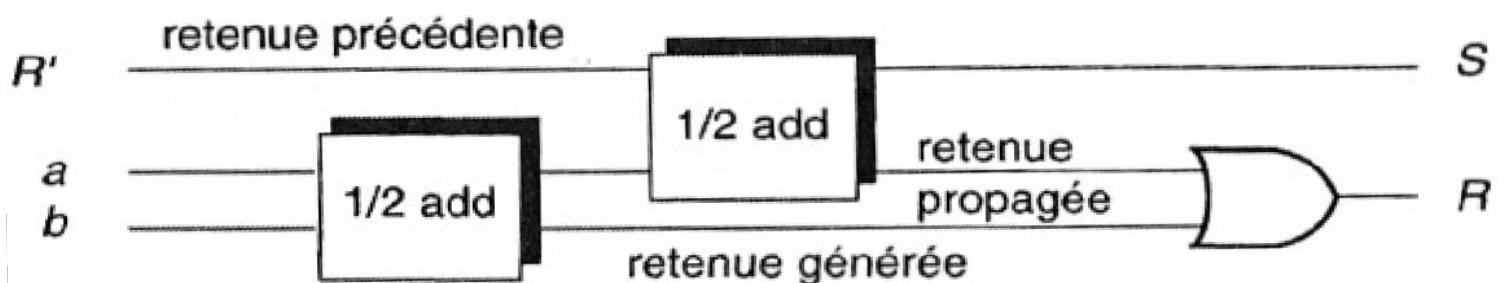

## 1.6.6. Exemple de synthèse (d'un additionneur binaire)

**Additionneur binaire:** circuit faisant la somme de 2 nombres binaires.

**Demi-additionneur:** additionneur ne tenant pas compte de la retenue éventuelle provenant d'une opération précédente.

$a \ b \mid S \ R$

-----

0 0 | 0 0

0 1 | 1 0

1 0 | 1 0

1 1 | 0 1

S: somme;

$$S = \bar{a} \cdot b + a \cdot \bar{b} = a \text{ xor } b$$

R = Retenue;      R = a.b

**Etage additionneur:**

**Additionneur complet:** utilisation en parallèle de plusieurs "étages additionneurs" (il faut autant d'étages que de bits dans chacun des nombres à additionner), chaque sortie d'un étage étant connecté à l'entrée de l'étage suivant.

Note: il faut attendre que la retenue se propage dans un étage pour activer celui-ci.

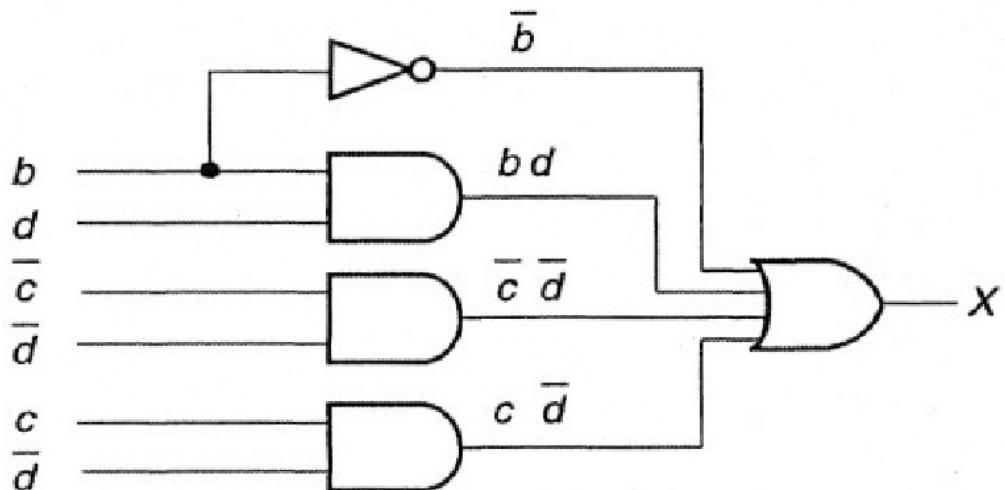

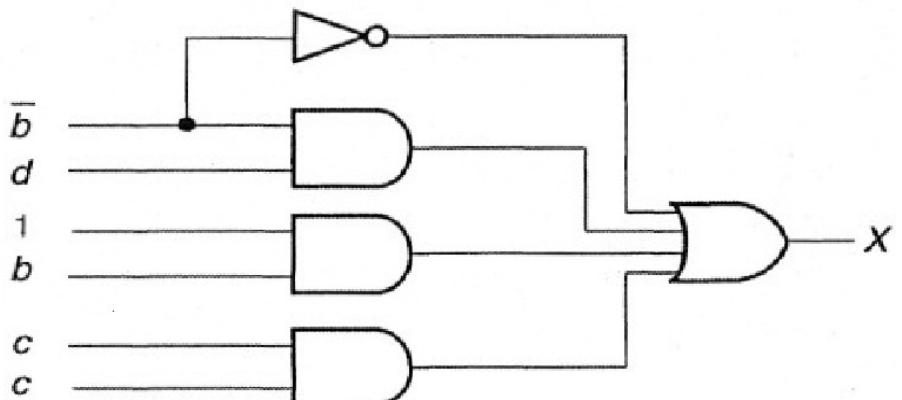

## 1.7. Analyse d'un circuit combinatoire

**Analyse:** retrouver la fonction d'un circuit dont on connaît uniquement le logigramme. Étapes:

1. trouver l'expression de **chaque fonction (sortie)** du circuit, en combinant chaque opérateur

2. pour chaque sortie, trouver la table de vérité et/ou une expression algébrique simplifiée

3. en déduire le rôle du circuit.

**Exemple:**

$$\begin{aligned}

X &= \bar{b} + b.d + \bar{c}.\bar{d} + c.\bar{d} = \bar{b} + b.d + \bar{d}.(\bar{c}+c) \\

&= \bar{b} + b.d + \bar{d} = \bar{b} + d + \bar{d} = \bar{b} + 1 = 1

\end{aligned}$$

Le rôle de ce circuit (fantaisiste) est de produire la constante 1.

**QWs "ao3wooclap". Quelle formule algébrique représente ce circuit ?**

- A)  $\bar{b} + d + c$       B)  $b + \bar{d} + c$

C)  $b + d$       D)  $b + c + d$

E) ni A, ni B, ni C, ni D

*Aide:*  $b + \bar{b}.d + 1.b + c =$

$b + \bar{b}.d + c =$

$(b+\bar{b}).(b+d) + c$

## 1.8. Démultiplexeur et multiplexeur

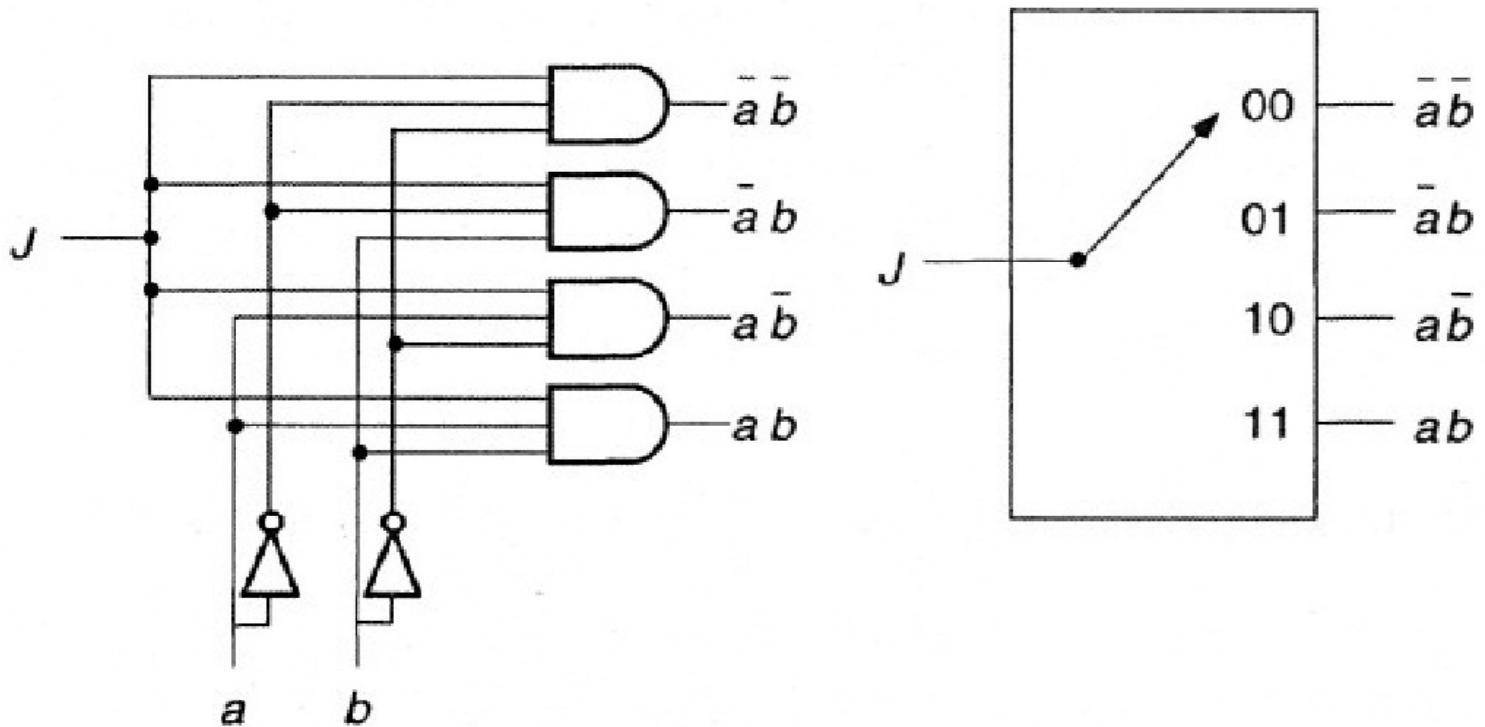

**Démultiplexeur (DEMUX) à N variables:** tout système combinatoire qui

- possède 1 ligne d'entrée, N lignes de commande (alias, contrôle, sélection), et  $2^N$  lignes de sortie correspondant aux  $2^N$  minterms des N variables des lignes de sélection (voir exemple ci-dessous),

- transmet l'entrée sur la ligne de sortie sélectionnée via les lignes de commande.

DEMUX à 2 variables (e.g., si  $a=b=0$ , il transmet l'entrée sur la sortie  $\bar{a}\bar{b}$ ):

**(QW) Dans un démultiplexeur à N variables de contrôle, les sorties correspondent aux ... ?**

- A)  $2^N$  minterms des N variables de contrôle

- B)  $2^N$  maxterms des N variables de contrôle

- C)  $2^N$  maxterms des N variables de contrôle

- D)  $2^N$  maxterms des N lignes d'entrée

- E) aucune des 4 dernières réponses n'est juste

## 1.8. Démultiplexeur et multiplexeur

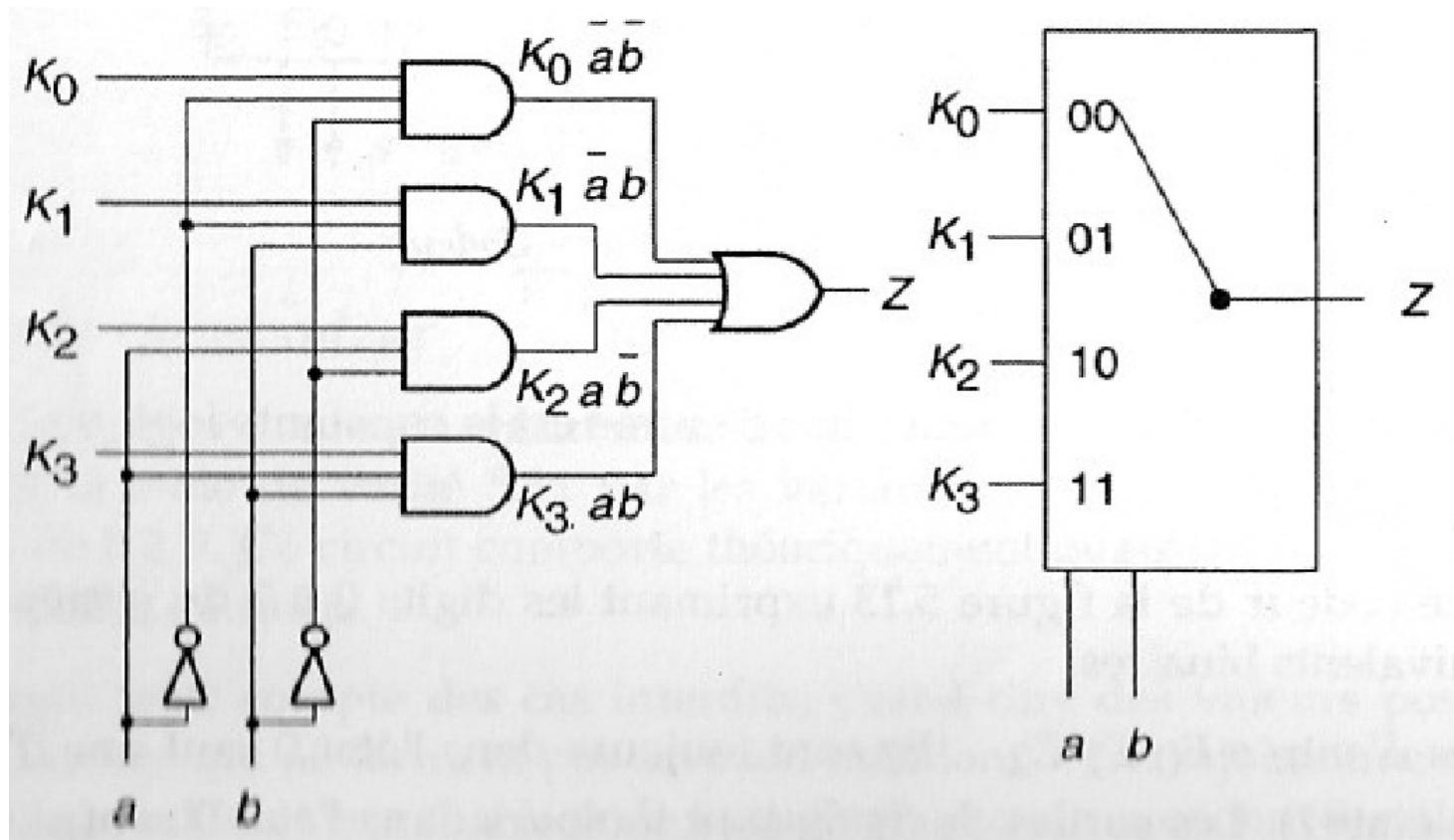

**Multiplexeur (MUX) à N variables:** tout système combinatoire qui

- possède 1 ligne de sortie, N lignes de commande/contrôle/sélection, et  $2^N$  lignes d'entrée correspondant aux  $2^N$  minterms des N variables des lignes de sélection (voir exemple ci-dessous),

- réalise la "fonction universelle", i.e., la pondération des  $2^N$  fonctions possibles par la ligne d'entrée pertinente (voir exemple ci-dessous).

*MUX à 2 variables:*  $\text{MUX}(a,b) = K_0 \cdot \bar{a} \cdot \bar{b} + K_1 \cdot \bar{a} \cdot b + K_2 \cdot a \cdot \bar{b} + K_3 \cdot a \cdot b$

En faisant varier les valeurs des lignes de commandes,

les  $2^N$  fonctions listées dans la section 1.2 peuvent être réalisées.

**(QW) Dans un multiplexeur (pas un démultiplexeur) à 2 variables de contrôle  $a$  et  $b$ , au moins une des sorties correspond à ... ?**

- A)  $a \cdot b$

- B)  $a \cdot \bar{b}$

- C)  $\bar{a} \cdot b$

- D) les 3 dernières réponses sont justes

- E) aucune des 4 dernières réponses n'est juste

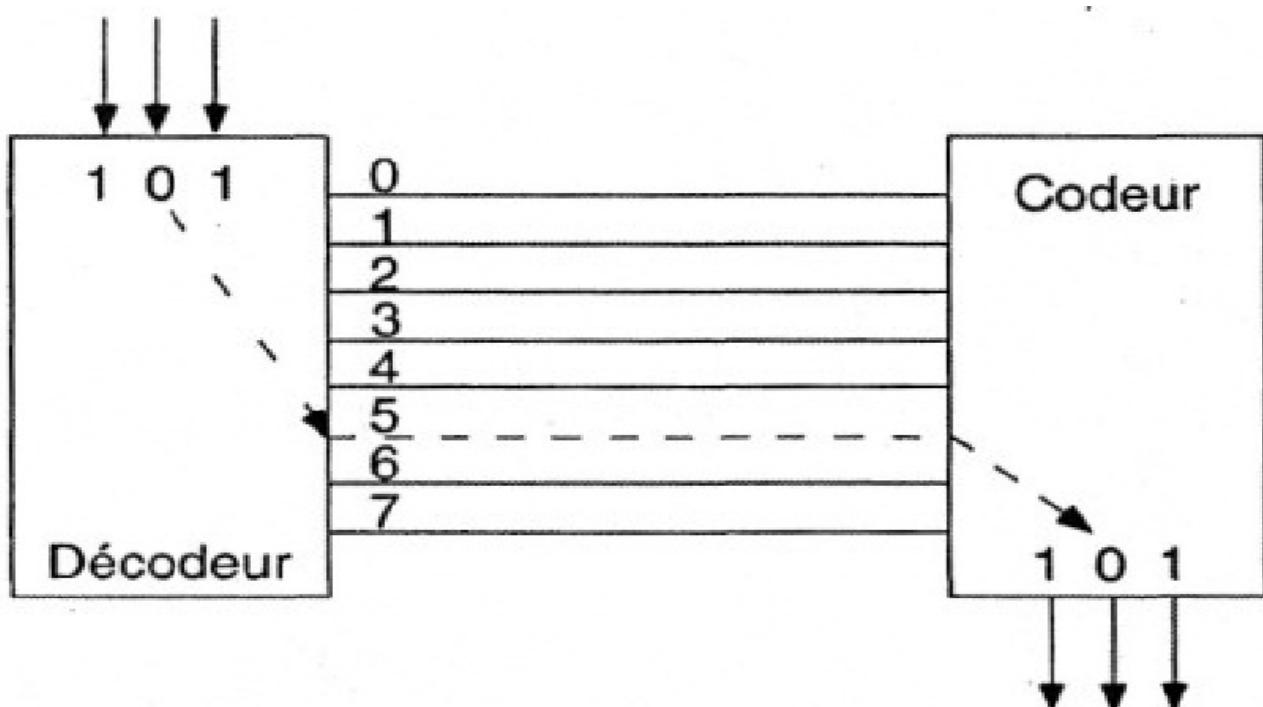

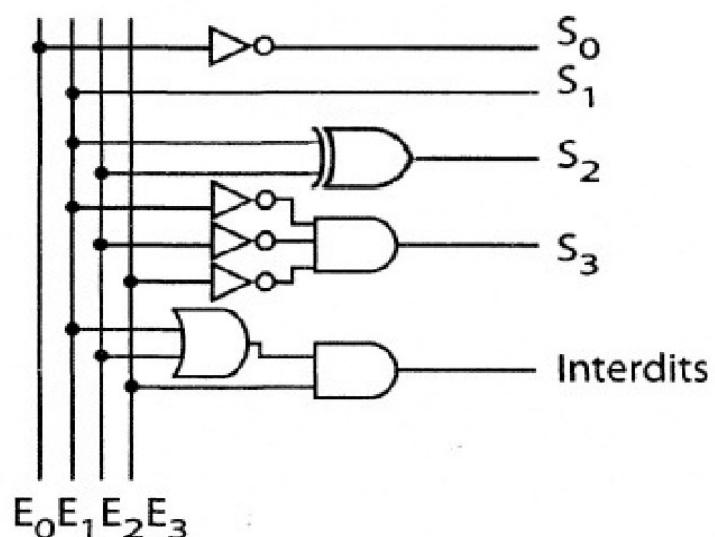

## 1.9. Codeur, décodeur, transcodeur

**Décodeur:** sorte de DEMUX dont l'état d'entrée est toujours 1

-> la ligne d'entrée usuelle du DEMUX n'existe pas et les lignes de commande sont alors appelées lignes d'entrée; plus précisément: compte-tenu du code sur les N lignes d'entrée/commande, 1 seule des  $2^N$  lignes de sortie est active.

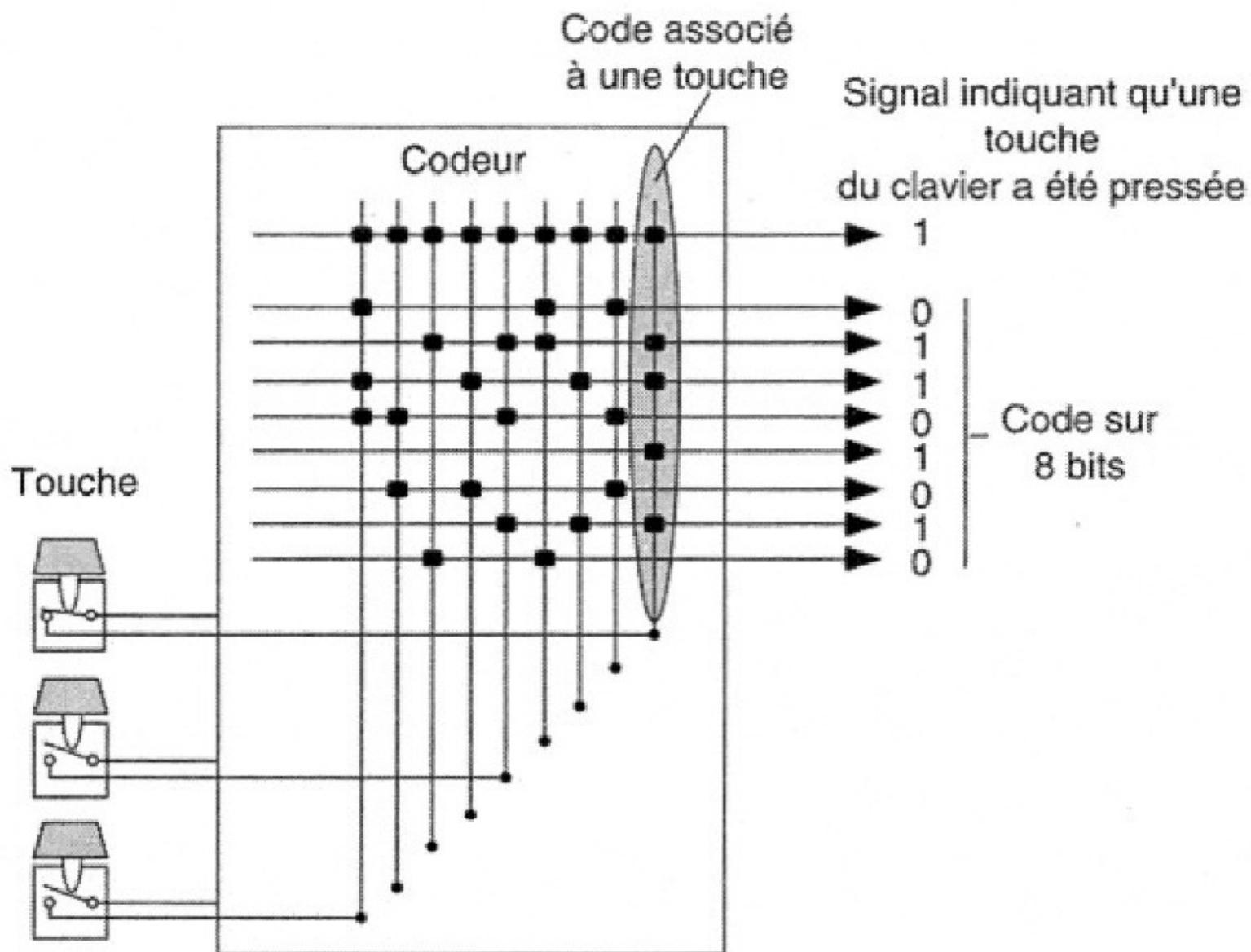

**Codeur:** inverse d'un décodeur (mais ce n'est pas un multiplexeur)

-> le code sur les N lignes de sortie correspond au rang de l'unique entrée active parmi les  $2^N$  entrées (voir exemple ci-dessous).

**Transcodeur:** à un code A sur N lignes d'entrée fait correspondre un code B sur m lignes de sortie.

**(QW) Si un décodeur a N entrées dont toutes sont à 1,**

**combien a t-il de sorties à 1 ?**    A) 1    B) N    C)  $2 * N$     D)  $2^N$

E) aucune des 4 dernières réponses n'est juste

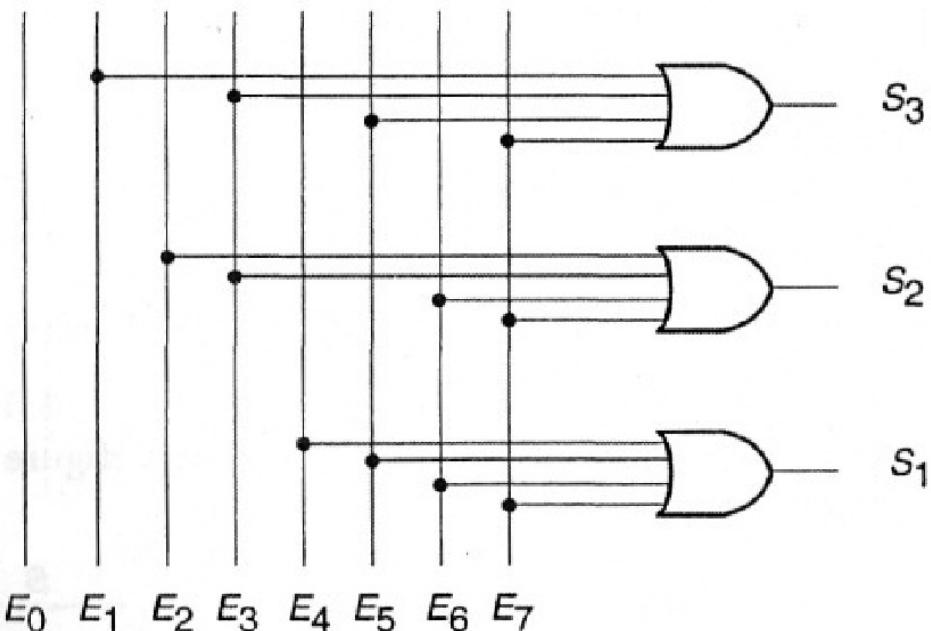

## 1.9. Exemple de codeur à 8 entrées

|   | $E_0$ | $E_1$ | $E_2$ | $E_3$ | $E_4$ | $E_5$ | $E_6$ | $E_7$ | $S_1$ | $S_2$ | $S_3$ |

|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0 | 1     |       |       |       |       |       |       |       | 0     | 0     | 0     |

| 1 |       | 1     |       |       |       |       |       |       | 0     | 0     | 1     |

| 2 |       |       | 1     |       |       |       |       |       | 0     | 1     | 0     |

| 3 |       |       |       | 1     |       |       |       |       | 0     | 1     | 1     |

| 4 |       |       |       |       | 1     |       |       |       | 1     | 0     | 0     |

| 5 |       |       |       |       |       | 1     |       |       | 1     | 0     | 1     |

| 6 |       |       |       |       |       |       | 1     |       | 1     | 1     | 0     |

| 7 |       |       |       |       |       |       |       | 1     | 1     | 1     | 1     |

$$S_1 = E_4 + E_5 + E_6 + E_7$$

$$S_2 = E_2 + E_3 + E_6 + E_7$$

$$S_3 = E_1 + E_3 + E_5 + E_7$$

QWs "ao3wooclap".

## 1.9. Exemple de codeur pour clavier

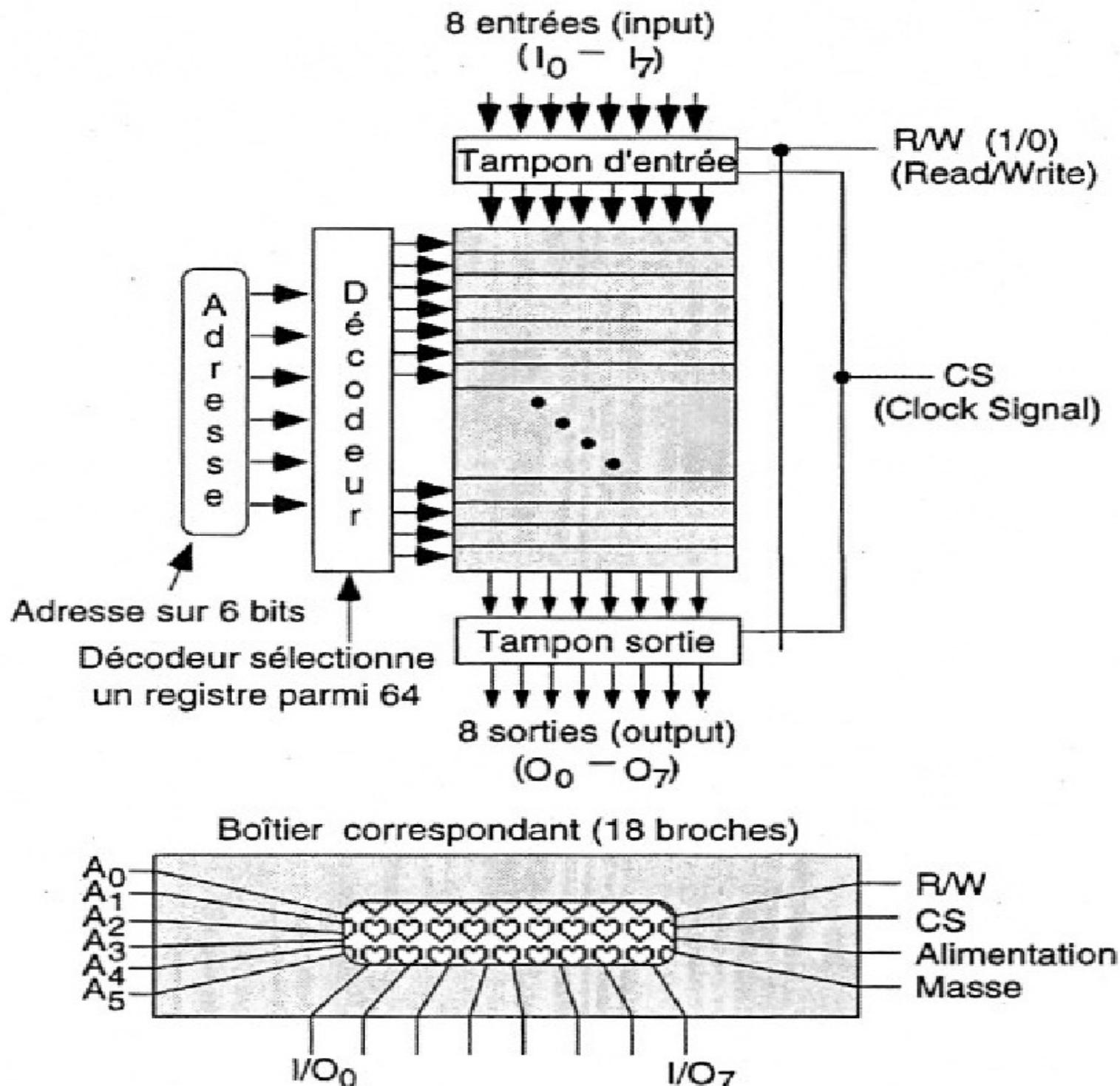

# 1.9. Utilisation d'un décodeur pour la mémoire centrale

Organisation d'une mémoire électronique de 64 mots de 8 bits:

## 2.1. Circuits séquentiels - définitions

**Circuit séquentiel:** circuit où le temps de propagation des signaux et la mémoire du circuit sont pris en compte

- > les signaux de sortie dépendent de signaux d'entrée précédents (-> notions d'états, de mémoire et de temps) et donc de rétroactions (retours des sorties dans les entrées)

- > étude via la théorie des automates finis.

**Automate fini:** fonction définie via une "fonction de transfert" ou une "table de transitions" ou encore un "diagramme d'états ou de transitions".

**Fonction de transfert:** la sortie  $S$ , et l'état  $Q$ , à l'instant  $t+1$ , dépendent de l'entrée et de l'état à l'instant  $t$ , i.e.,

$$S(t+1) = f(Q(t), E(t)) \quad \text{et} \quad Q(t+1) = g(Q(t), E(t))$$

**Table de transition (ou d'états):** les tables des fonctions  $f$  et  $g$  ci-dessus déterminent les valeurs de  $Q(t+1)$  et  $S(t+1)$  pour chaque combinaison de valeurs de  $E(t)$  et  $Q(t)$ .

**Diagrammes d'états ou de transitions:** les états y sont représentés par des ronds, et les transitions entre états par des flèches.

Exemple de question d'évaluation: **Dans une fonction de transfert ...**

- A) la sortie  $S$  à l'instant  $t$  dépend de l'entrée et de l'état à l'instant  $t$

- B) l'état  $Q$  à l'instant  $t$  dépend de l'entrée et de l'état à l'instant  $t$

- C) l'état  $Q$  à l'instant  $t$  dépend de l'entrée à l'instant  $t$

- D) les 3 dernières réponses sont justes

- E) aucune des 4 dernières réponses n'est juste

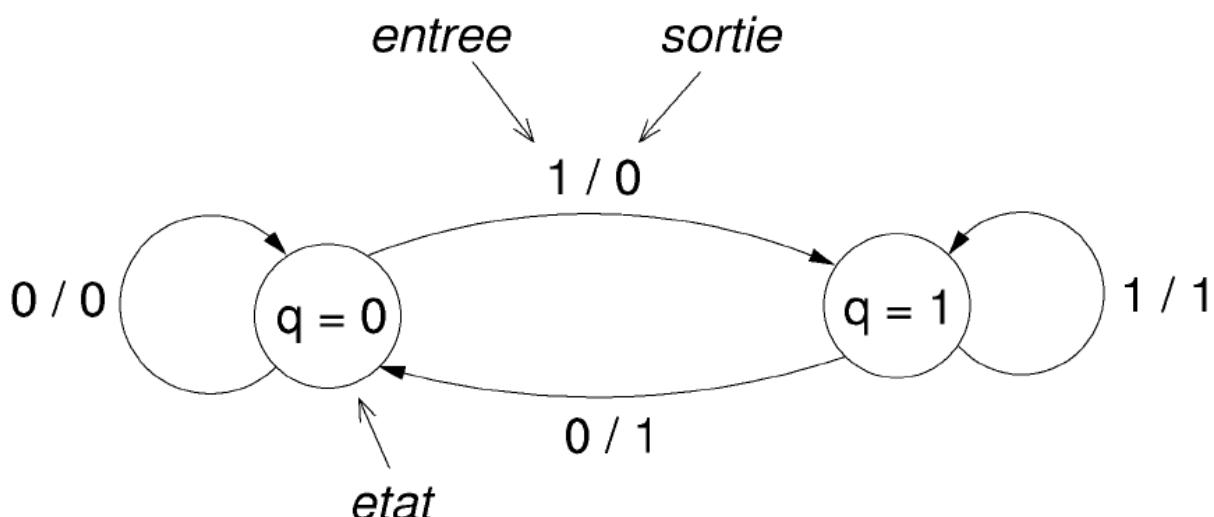

## 2.2. Exemple d'automate fini

**MÉMOIRE BINAIRE (→ stocke 1 bit):** 1 entrée à mémoriser,

2 états (0 ou 1).

## **Fonction de transfert**

- $S(t+1) = Q(t)$  : la sortie  $S$  à l'instant  $t+1$  est égale à l'état  $Q$  à l'instant  $t$

- $Q(t+1) = E(t)$  : l'état  $Q$  à l'instant  $t+1$  est égal à l'entrée à l'instant  $t$ .

**Tables de transitions:** valeurs de  $Q(t+1)$  et  $S(t+1)$  en fonction de  $E(t)$  et  $Q(t)$

$$\begin{array}{c}

\textbf{S(t+1)} \\

\backslash E(t) | 0 \ 1 \\

Q(t) ---+--- \\

0 | 0 \ 0 \\

1 | 1 \ 1

\end{array}

\qquad

\begin{array}{c}

\textbf{Q(t+1)} \\

\backslash E(t) | 0 \ 1 \\

Q(t) ---+--- \\

0 | 0 \ 1 \\

1 | 0 \ 1

\end{array}$$

### **Diagramme d'états/transitions:**

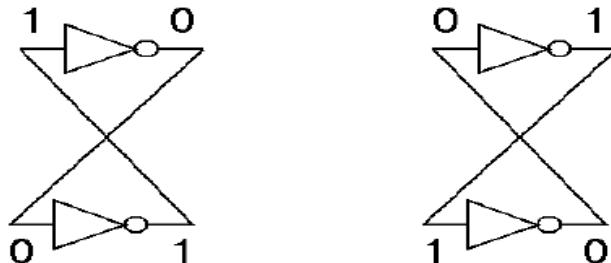

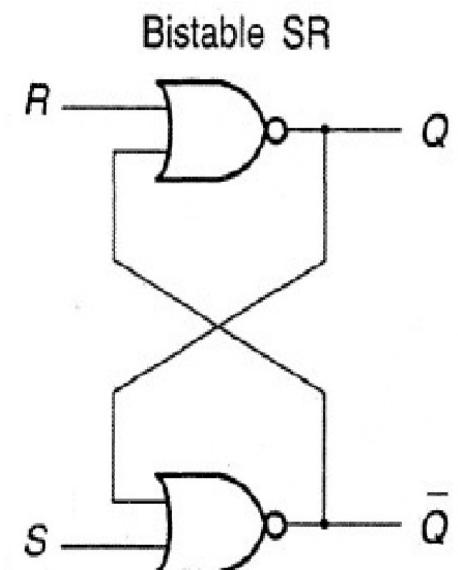

## 2.3. Bistables et bascules

**Bistable**: automate ayant 2 états stables.

Exemple pour illustrer

le principe: 2 inverseurs

en opposition.

**Bascule**: circuit mettant en œuvre un bistable; bascules D, SR, JK et T.

**Bascule asynchrone**: la sortie change dès que le signal d'entrée change.

**Bascule synchrone** (e.g., D et SR):

bascule avec une entrée "horloge" [clock] ;

la sortie ne change que lorsque l'entrée C [Clock, Control] est activée (à 1).

**Bascule synchrone sur front** [flip-flop]:

le calcul s'effectue de nouveau lorsque le signal d'horloge change de valeur

(front montant: passage de 0 à 1; front descendant: passage de 1 à 0).

**Bascule synchrone sur niveau** [latch]: le calcul des sorties et de l'état

s'effectue de nouveau lorsque le signal d'horloge a atteint 1 ou 0.

Exemple de question d'évaluation:

**Dans certaines bascules "synchrone sur front" ...**

- A) la sortie peut changer lorsque le signal d'horloge passe de 0 à 1

- B) la sortie peut changer lorsque le signal d'horloge passe de 1 à 0

- C) les 2 dernières réponses sont justes

- D) la sortie change lorsque que le signal d'horloge a atteint 1 ou 0

- E) aucune des 4 dernières réponses n'est juste

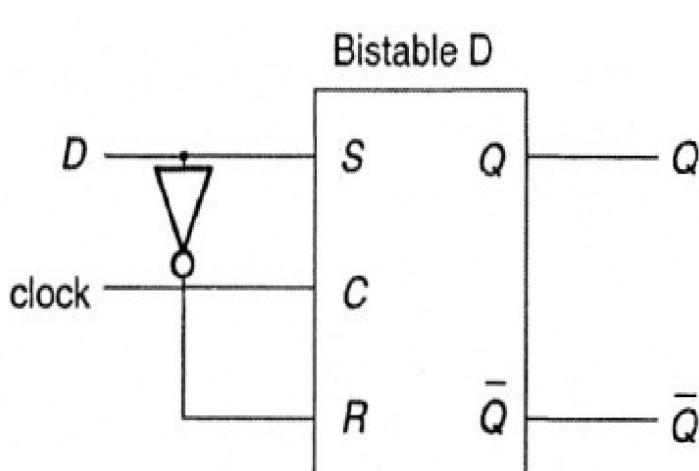

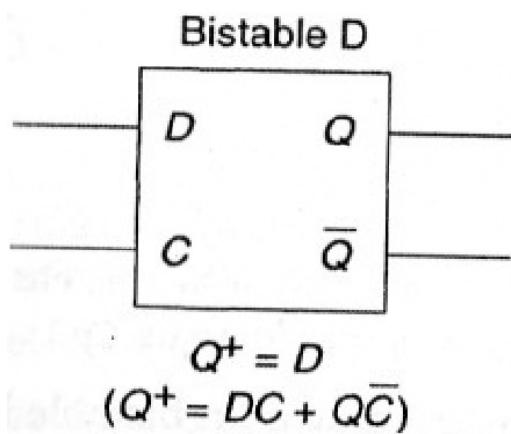

## 2.3.1. Bascules D et SR

**Bascule/bistable D [Delay]:** recopie, sur sa sortie Q, le signal d'entrée D avec un retard d'une période d'horloge;

si C=1,  $Q^+ = Q(t+1) = D$ ;

si C=0, Q ne change pas.

Donc:  $Q^+ = D \cdot C + Q \cdot \bar{C}$

*Ceci peut être réalisé avec une bascule SR (exemple ci-dessous).*

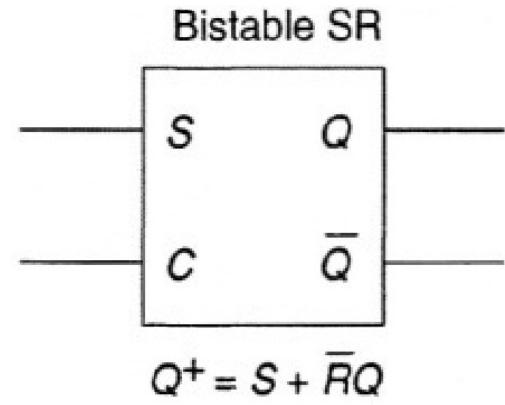

**Bascule/bistable SR [Set-Reset]:**  $Q^+ = S + Q \cdot \bar{R}$

S et R ne doivent pas être tous deux à 1 car sinon Q et  $\bar{Q}$  sont tous deux à 0

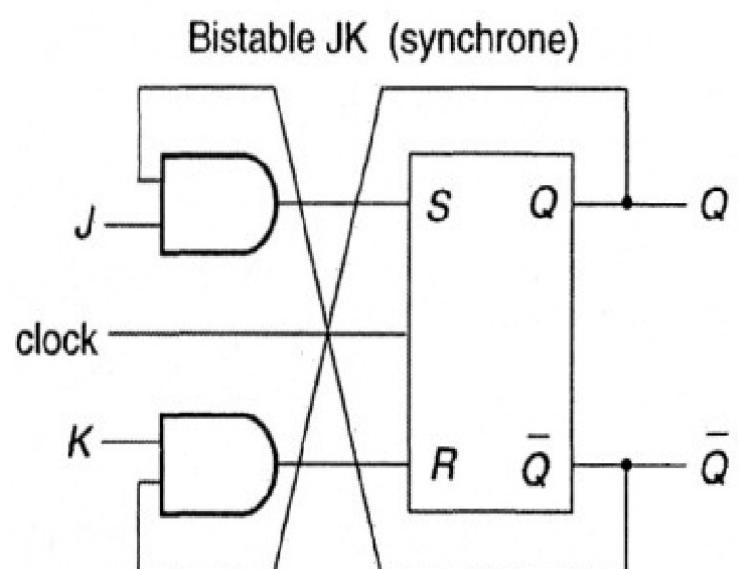

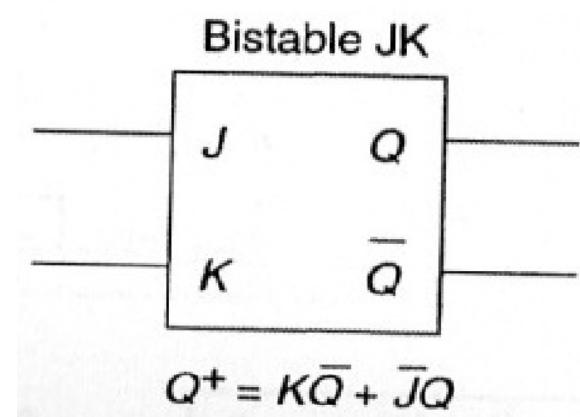

## 2.3.2. Bascules T et JK

**Bascule/bistable JK:** proche variante de SR avec  $J=S$  et  $K=R$ ;

$$Q^+ = J \cdot \bar{Q} + \bar{K} \cdot Q \quad (\text{rappel: pour SR, } Q^+ = S + \bar{R} \cdot Q).$$

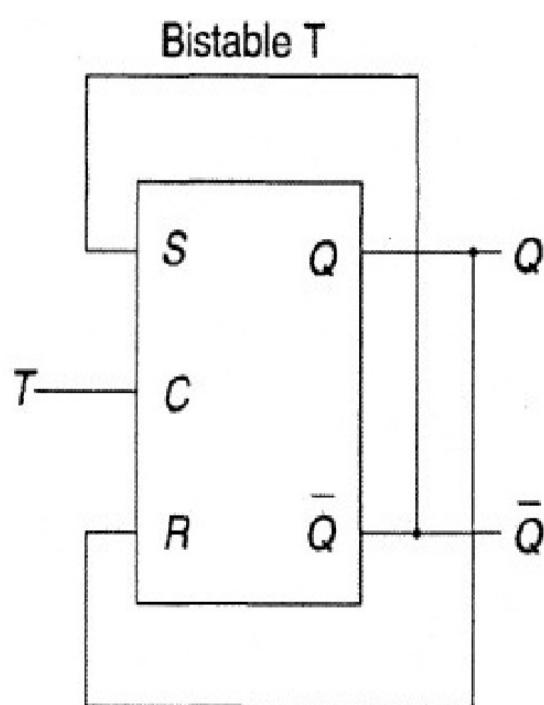

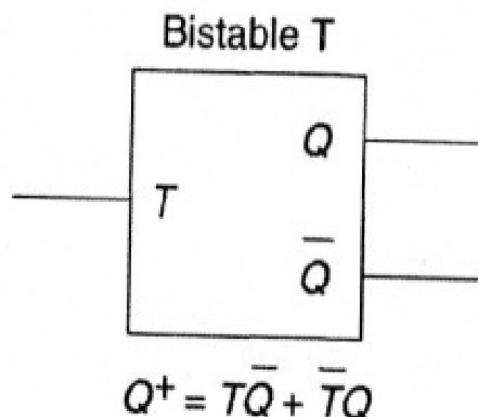

**Bascule/bistable T [Trigger flip-flop] (bascule à déclenchement):**

si  $T=1$ , inversion des entrées/sorties;

si  $T=0$ ,  $Q$  ne change pas.

$$Q^+ = T \cdot \bar{Q} + \bar{T} \cdot Q$$

Ceci peut être réalisé avec une bascule SR (exemple ci-dessous).

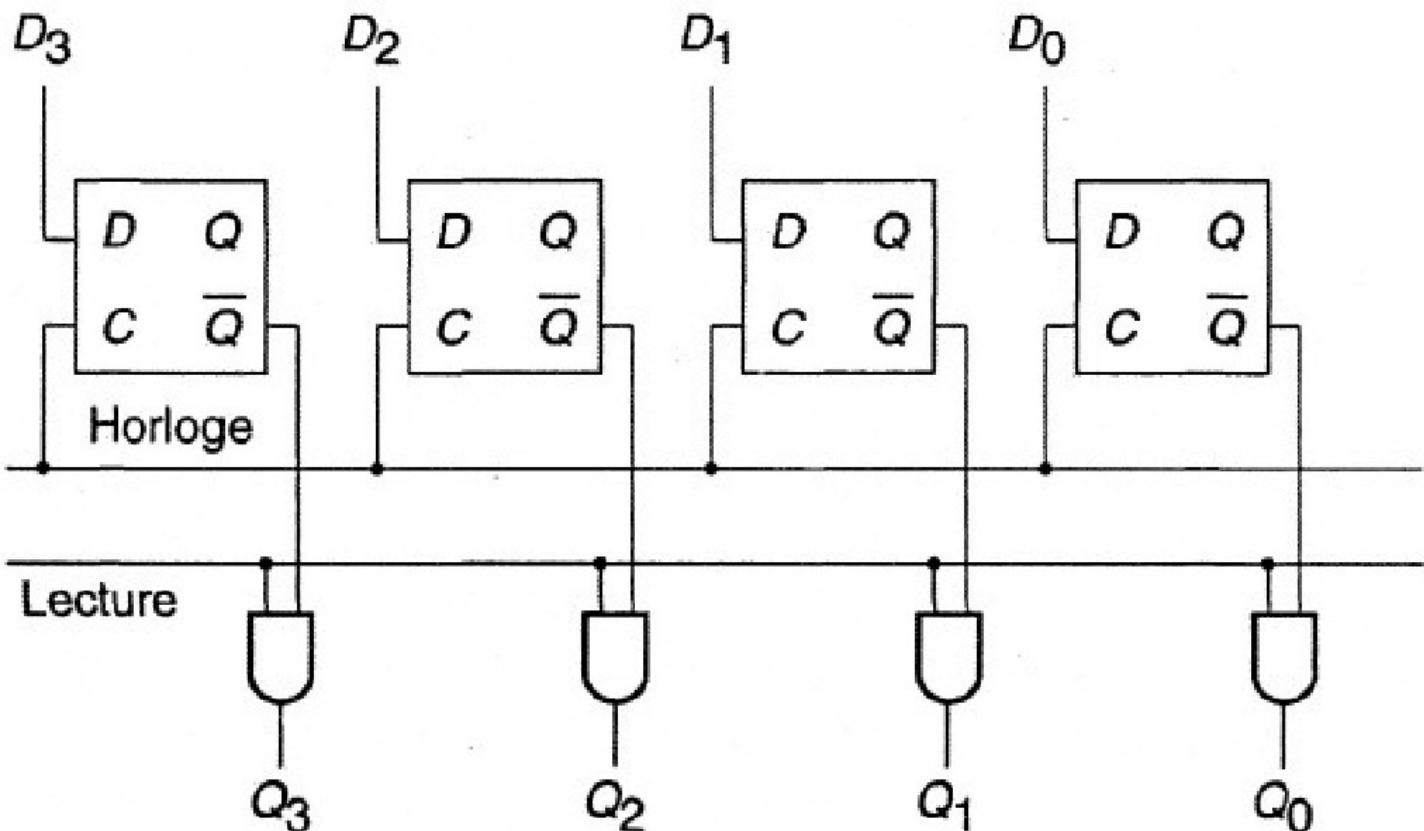

## 2.3.4. Utilisation de bascules pour créer un registre

Registre 4 bits

Exemple de question d'évaluation:

- Pour une bascule T avec une entrée t, un état q et une sortie q+, on a ...**

- A)  $q^+ = t \cdot \text{non}(q) + \text{non}(t) \cdot q$

- B)  $q^+ = \text{non}(t \cdot q) + \text{non}(t + q)$

- C)  $q^+ = \text{non}(t) \cdot q + t \cdot \text{non}(q)$

- D)  $q^+ = \text{non}(t) \cdot \text{non}(q) + t \cdot q$

- E) aucune des 4 réponses précédentes n'est juste

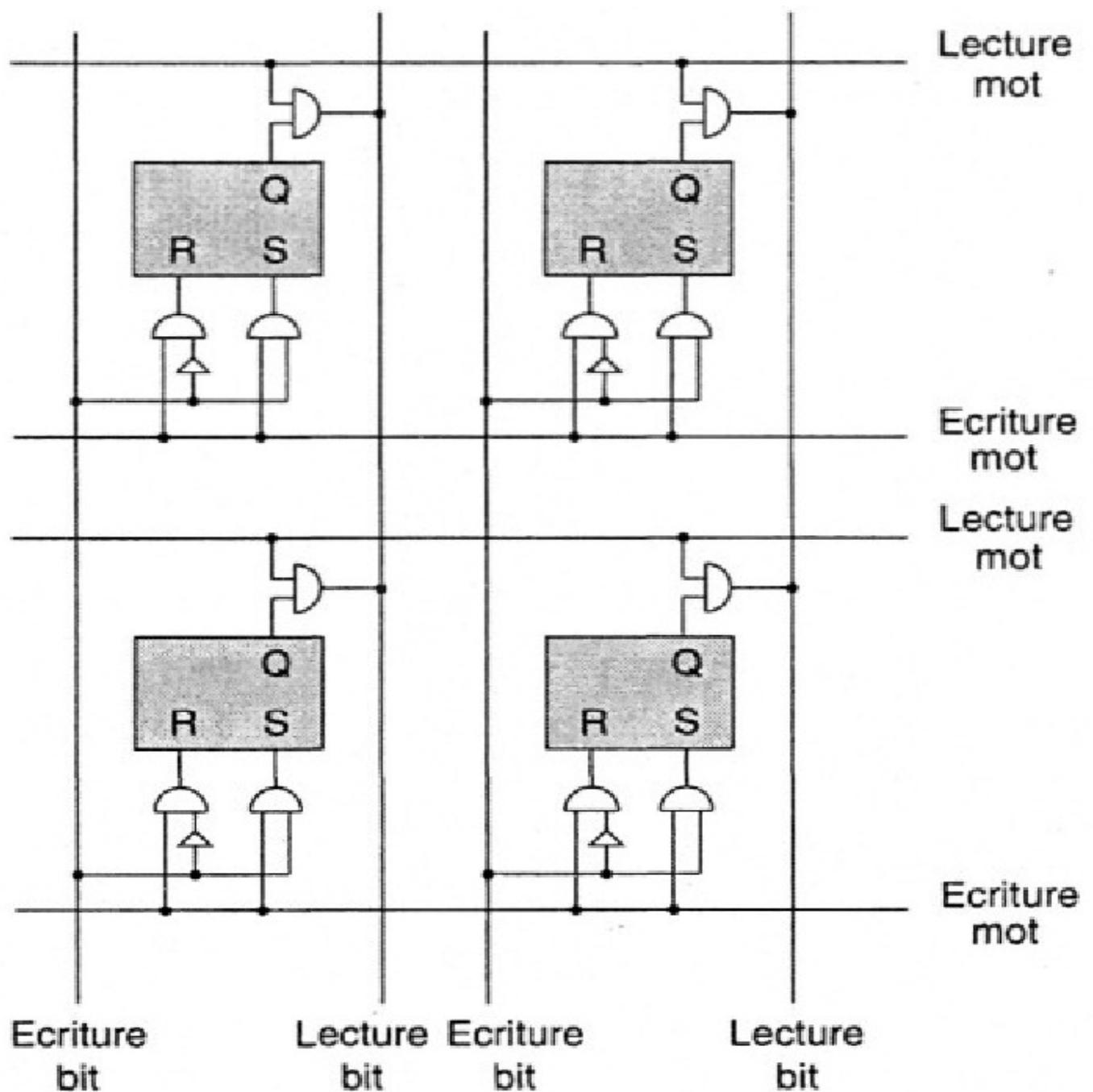

## 2.3.5. Utilisation de bascules pour la mémoire centrale

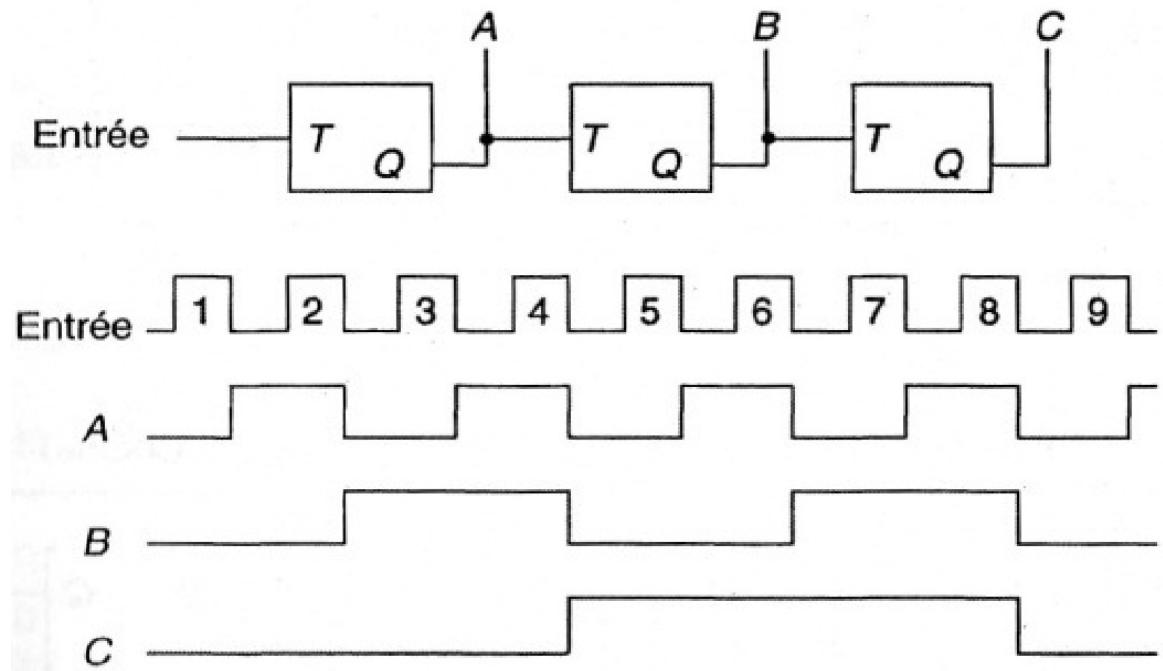

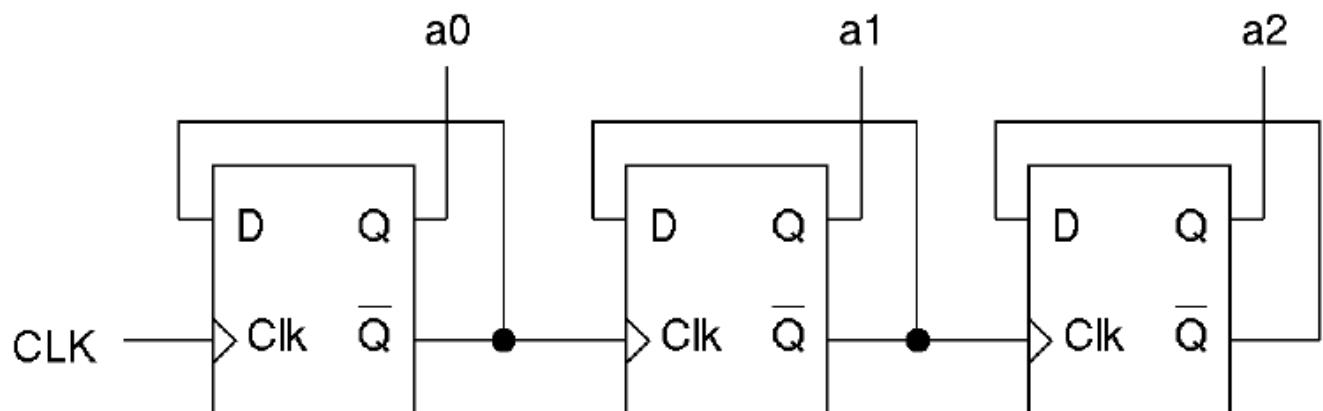

## 2.3.6. Utilisation de bascules pour créer un compteur à 3 bits

Avec 3 bascules T:

Avec 3 bascules D:

## 2.4. Synthèse d'un circuit séquentiel

**Procédure pour la synthèse d'un circuit séquentiel:**

1. pour toute entrée, décrire la fonction (réponse) du circuit via un diagramme de transition

2. construire la table d'états en indiquant toutes les entrées et sorties

3. réaliser les circuits combinatoires pour chaque bascule et chaque sortie

4. dessiner le circuit

**Exemple: réaliser un compteur cyclique sur 2 bits**

-> sortie: 00, 01, 10, 11, 00, ...

entrée:  $X=1$  -> incrémentation;  $X=0$  -> pas de changement

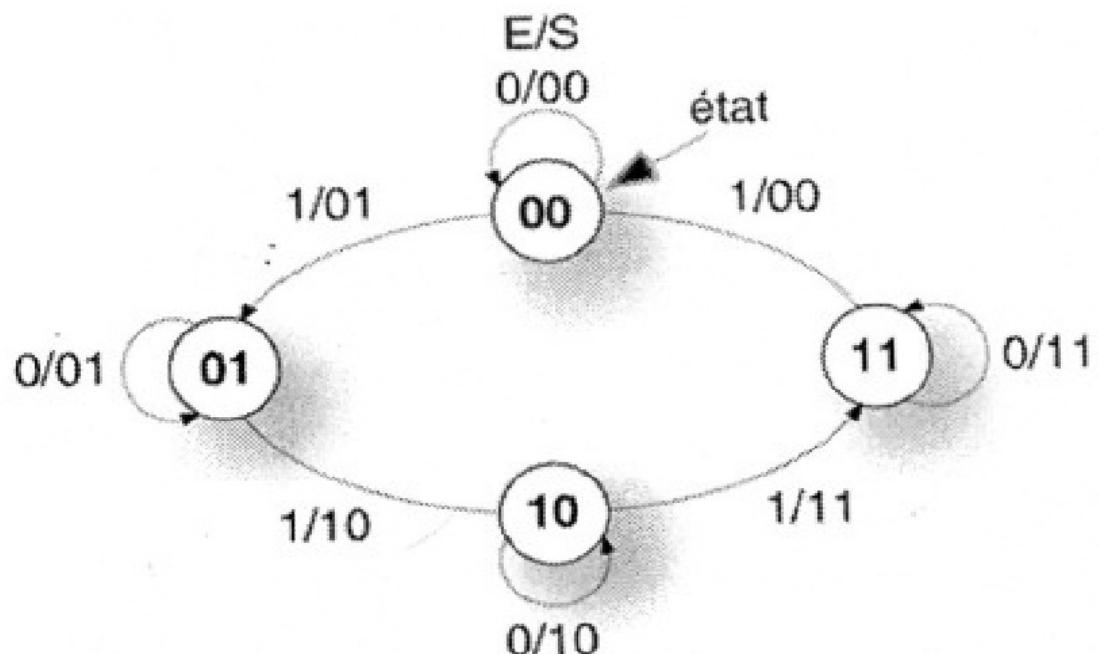

**Diagramme de transition:**

## 2.4.1. Exemple: réaliser un compteur 2 bits

### Table de transition:

Les 2 bits du compteur sont à mémoriser

-> 2 bascules T (choix semi-arbitraire)

(rappel: si  $T=1$ , inversion des entrées/sorties;

si  $T=0$ , Q ne change pas), donc:

$T_0$  doit être égal à 1 si  $Q_0$  change

$T_1$  doit être égal à 1 si  $Q_1$  change

Les sorties sont égales aux états futurs:  $S_0 = Q_0^+$  et  $S_1 = Q_1^+$

| états<br>présents |       |     | entrée | états futurs |         | entrées des<br>bistables |       | sorties |  |       |       |

|-------------------|-------|-----|--------|--------------|---------|--------------------------|-------|---------|--|-------|-------|

| $Q_1$             | $Q_0$ | $X$ |        | $Q_1^+$      | $Q_0^+$ |                          | $T_1$ | $T_0$   |  | $S_1$ | $S_0$ |

| 0                 | 0     | 0   |        | 0            | 0       |                          | 0     | 0       |  | 0     | 0     |

| 0                 | 0     | 1   |        | 0            | 1       |                          | 0     | 1       |  | 0     | 1     |

| 0                 | 1     | 0   |        | 0            | 1       |                          | 0     | 0       |  | 0     | 1     |

| 0                 | 1     | 1   |        | 1            | 0       |                          | 1     | 1       |  | 1     | 0     |

| 1                 | 0     | 0   |        | 1            | 0       |                          | 0     | 0       |  | 1     | 0     |

| 1                 | 0     | 1   |        | 1            | 1       |                          | 0     | 1       |  | 1     | 1     |

| 1                 | 1     | 0   |        | 1            | 1       |                          | 0     | 0       |  | 1     | 1     |

| 1                 | 1     | 1   |        | 0            | 0       |                          | 1     | 1       |  | 0     | 0     |

-> circuit à ajouter avant les bascules pour transformer X,  $Q_0$  et  $Q_1$  en  $T_0$  et  $T_1$ :

$$T_1 = \overline{Q_1} \ Q_0 \ X + Q_1 \ Q_0 \ X = X \ (\overline{Q_1} \ Q_0 + Q_1 \ Q_0) = X \ (Q_0 \ (\overline{Q_1} + Q_1)) = X \ Q_0$$

$$T_0 = \overline{Q_1} \ Q_0 \ X + \overline{Q_1} \ Q_0 \ X + Q_1 \ \overline{Q_0} \ X + Q_1 \ Q_0 \ X$$

$$T_0 = X \ (\overline{Q_1} \ (\overline{Q_0} + Q_0) + Q_1 \ (\overline{Q_0} + Q_0))$$

$$T_0 = X$$

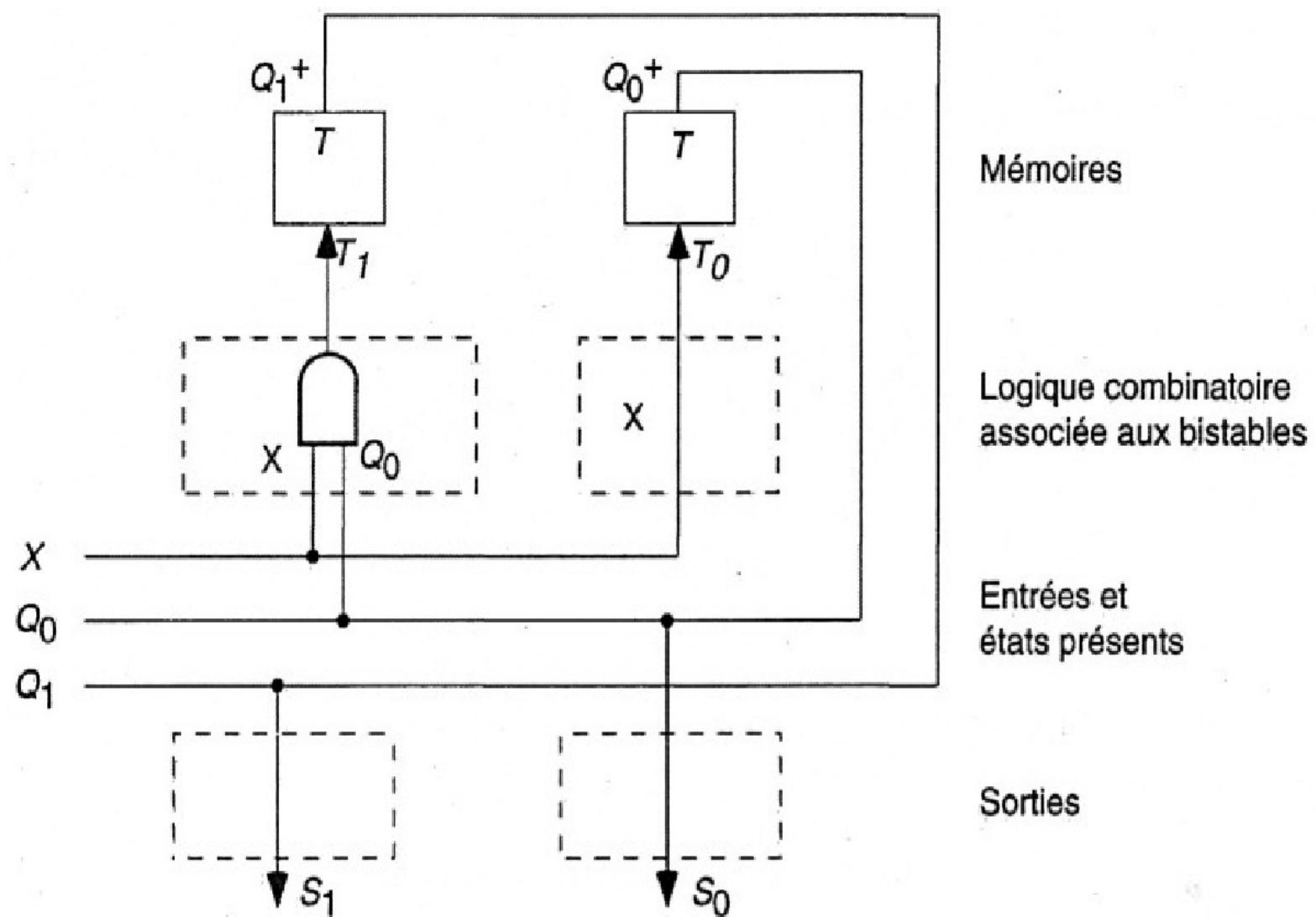

## 2.4.1. Exemple: réaliser un compteur 2 bits

*Logigramme:*

Mémoires

Logique combinatoire

associée aux bistables

Entrées et

états présents

Sorties

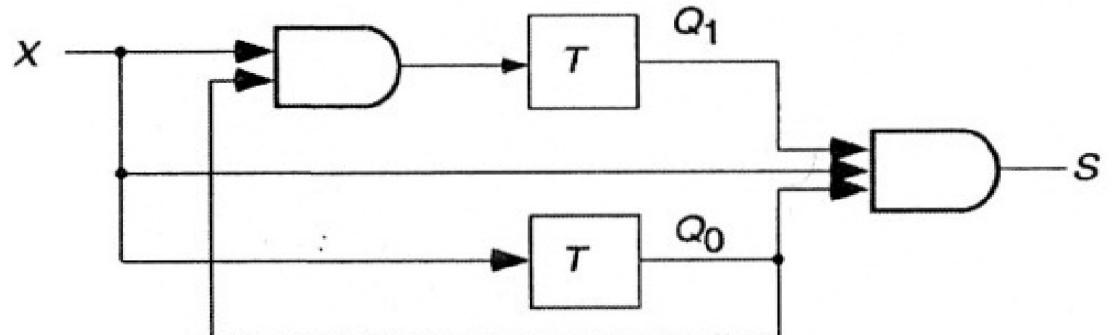

## 2.5. Analyse d'un circuit séquentiel

- Étapes:**

1. mettre le circuit sous sa forme normale

2. déterminer sa table d'état, son diagramme de transition, ou ses fonctions de transfert

Exemple de circuit à analyser:

Table d'états:

| états présents |       | entrée | états futurs |          | entrées des bistables |       | sortie |  |

|----------------|-------|--------|--------------|----------|-----------------------|-------|--------|--|

| $Q_1$          | $Q_0$ | $X$    | $Q^{+1}$     | $Q^{+0}$ | $T_1$                 | $T_0$ | $S$    |  |

| 0              | 0     | 0      | 0            | 0        | 0                     | 0     | 0      |  |

| 0              | 0     | 1      | 0            | 1        | 0                     | 1     | 0      |  |

| 0              | 1     | 0      | 0            | 1        | 0                     | 0     | 0      |  |

| 0              | 1     | 1      | 1            | 0        | 1                     | 1     | 0      |  |

| 1              | 0     | 0      | 1            | 0        | 0                     | 0     | 0      |  |

| 1              | 0     | 1      | 1            | 1        | 0                     | 1     | 0      |  |

| 1              | 1     | 0      | 1            | 1        | 0                     | 0     | 0      |  |

| 1              | 1     | 1      | 0            | 0        | 1                     | 1     | 1      |  |

$$Q^{+1} = Q_1 \text{ xor } T_1, \quad Q^{+0} = Q_0 \text{ xor } T_0, \quad S = Q_1 \cdot Q_0 \cdot X, \quad T_1 = X \cdot Q_0, \quad T_0 = X$$

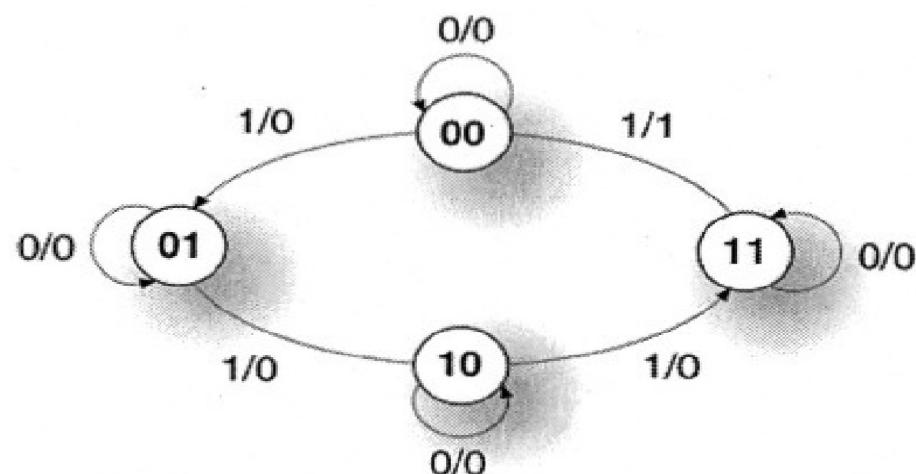

Diagramme de transition:

**Conclusion:** ce circuit est un diviseur par 4, i.e., la sortie est à 1 dès qu'il y a eu 4 impulsions ( $X=1$ ) sur l'entrée X.

### 3. TD pour cette partie 3 du cours d'A.O.

#### I. Exercices rapides de contrôle d'apprentissage

1. Cf. les exemples de question d'évaluation dont la solution n'a pas été donnée en CM

2. Réaliser les fonctions logiques suivantes avec des portes NAND:

a)  $\bar{A}$       b)  $A \cdot B$       c)  $A + B$

3. Vérifier que les relations suivantes sont vraies:

a)  $a + (\bar{a} \cdot b) = a + b$

b)  $a \cdot (a + b) = a$

c)  $a + (a \cdot b) = a$

d)  $(a + \bar{b}) \cdot (a + b) = a$

4. La formule "  $p \cdot (\bar{p} \cdot q \cdot r)$  " est-elle toujours fausse ?

## Circuits combinatoires

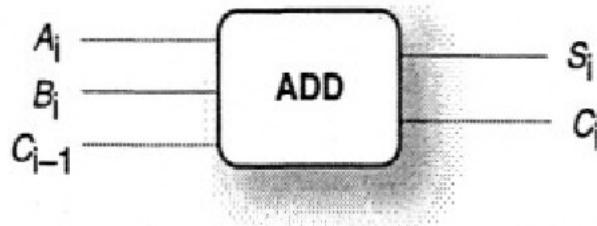

1. Synthèse d'un additionneur binaire : un additionneur binaire est un dispositif effectuant la somme  $S_i$  de deux bits  $A_i$  et  $B_i$  d'ordre  $i$  et d'une retenue  $C_{i-1}$  d'ordre  $i-1$  immédiatement inférieur. On le symbolise de la façon suivante (figure 5.30) :

Figure 5.30 : Additionneur symbolisé

- a) Donner la table de vérité.

- b) Déduire et simplifier les expressions booléennes pour les variables de sortie.

- c) Réaliser le circuit équivalent.

2. Construire un circuit logique susceptible de comparer entre eux deux nombres binaires. En entrée, on dispose de deux nombres de trois bits chacun :  $A_2\ A_1\ A_0$  et  $B_2\ B_1\ B_0$ . En sortie, on aimerait avoir : 1 si  $A_2\ A_1\ A_0 = B_2\ B_1\ B_0$ , 0 sinon.

- ↗ On demande un circuit optimisé, c'est-à-dire avec un nombre minimum d'opérateurs logiques choisis parmi les opérateurs NON, ET, OU, OU EXCLUSIF.

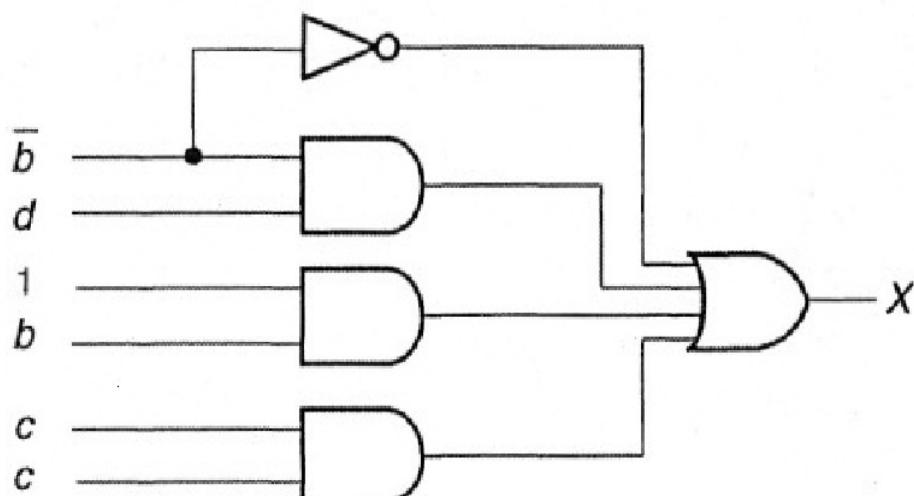

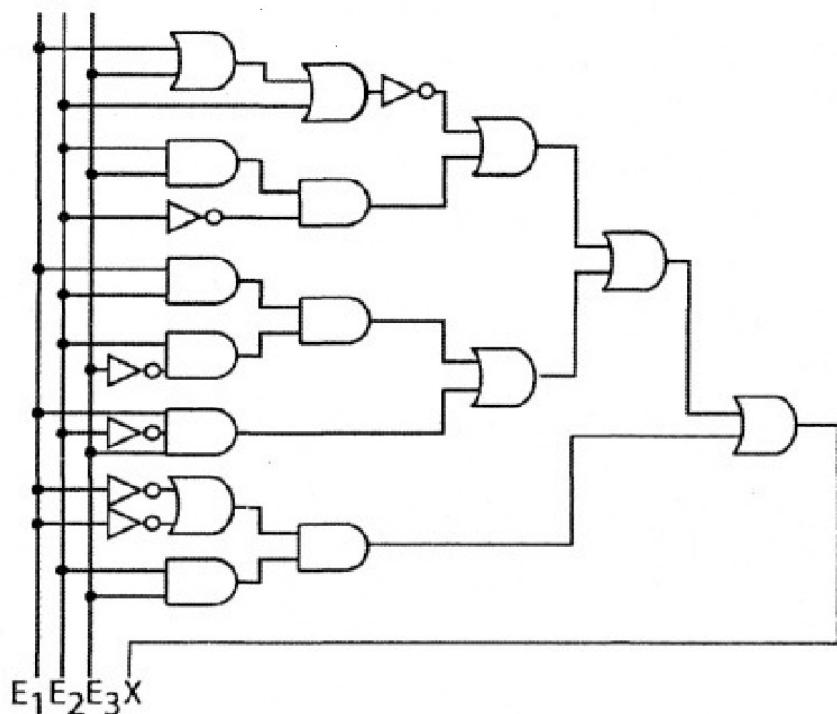

3. Analyser le circuit logique de la figure 5.31.

Figure 5.31 : Logigramme du circuit à analyser (exercice 3)

Donner :

- a) l'expression booléenne correspondant à la sortie  $X$ ,

- b) l'expression simplifiée et le circuit correspondant en n'utilisant que des opérateurs logiques à deux entrées choisis parmi les suivants : ET, OU, OU EXCLUSIF, ainsi que l'opérateur NON,

- c) la table de vérité,

- d) le rôle de ce circuit.

#### 4. Analyser le circuit de la figure 5.32.

Figure 5.32 : Logigramme du circuit à analyser (exercice 4)

Donner :

- a) les expressions logiques des sorties;

- b) la table de vérité;

- c) le rôle du circuit.

## Circuits séquentiels

5.

Synthèse d'un soustracteur série : ce circuit doit avoir :

- deux entrées externes  $A_i$  et  $B_i$  (= 2 digits de même poids à soustraire),

- 1 bistable S-R dont l'état correspond à la retenue précédente  $C_{i-1}$ ,

- 1 sortie  $X_i = A_i - (B_i + C_{i-1})$

Déterminer :

- le diagramme de transition;

- la table d'états;

- le circuit sous sa forme normale.

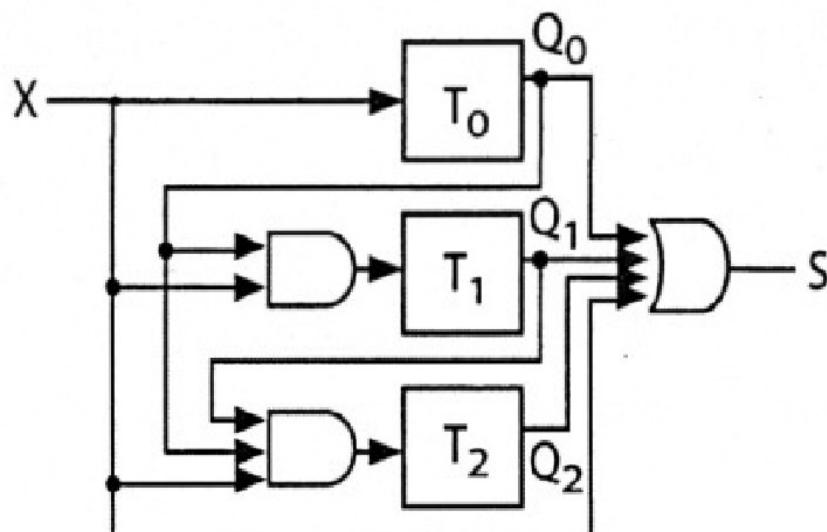

6.

Analyser le circuit de la figure 5.33, composé de : 1 entrée  $X$ , 3 bistables ( $T_0$ ,  $T_1$ ,  $T_2$ ) et 1 sortie  $S$ . Ce circuit correspond au modèle de Mealy, donc  $S = f(X, Q_2, Q_1, Q_0)$ .

Figure 5.33 : Circuit à analyser

- Mettre le circuit sous la forme normale,

- remplir la table d'états complète,

- déduire le diagramme de transition,

- spécifier le rôle de ce circuit.

**Explication supplémentaire.** Le dessin de l'énoncé de ce dernier exercice correspond à un "automate de Moore": les sorties à l'instant  $t+1$  tiennent compte des états à l'instant  $t+1$ , i.e., les nouveaux états sont d'abord calculés et ensuite les sorties sont calculées. La question "a)" demande une conversion en "automate de Mealy", i.e., un automate dont les sorties à l'instant  $t+1$  tiennent aussi directement compte des entrées à l'instant  $t$ , i.e., les nouveaux états et les sorties sont calculées en parallèle. Ce dernier automate est plus général mais il impose que les bascules T aient une entrée CLOCK supplémentaire pour permettre la synchronisation.

### Exemples de questions de QCM pour cette partie 3

#### 1. Qu'est-ce qu'un circuit séquentiel ?

- A) un circuit où le temps de propagation des signaux et la mémoire du circuit sont pris en compte

- B) un circuit dont les sorties peuvent aussi être ses entrées

- C) un circuit qui s'étudie via la théorie des automates finis

- D) les 3 dernières réponses

- E) aucune des 4 dernières réponses

#### 2. Quelle formule algébrique représente le circuit suivant ?

- A)  $\bar{b} + d + c$

- B)  $b + \bar{d} + c$

- C)  $b + d$

- D)  $b + c + d$

- E) aucune des 4 dernières réponses

#### 3. Combien de fonctions logiques peuvent être représentées avec des tables de vérité à $V$ variables d'entrée ?

- A)  $2^*V$  fonctions

- B)  $2^V$  fonctions

- C)  $2^N$  fonctions, avec  $N = 2^V$

- D) les 3 dernières réponses

- E) aucune des 4 dernières réponses

#### 4. La table de vérité suivante est celle du ... ?

- A) XOR

- B) NAND

- C) NOR

- D) OR

- E) aucune des 4 dernières réponses

| a | b |  | f(a, b) |

|---|---|--|---------|

| 0 | 0 |  | 0       |

| 0 | 1 |  | 1       |

| 1 | 0 |  | 0       |

| 1 | 1 |  | 0       |

#### 5. L'expression $a + (a \cdot b) = a$ est vraie ?

- A) seulement quand a est vrai

- B) par exemple quand a est vrai

- C) par exemple quand  $a + (\bar{a} \cdot b) = a + b$

- D) toujours

- E) les 3 dernières réponses

#### 6. Un exemple d'opérateur qui peut avoir plus de deux entrées est ...

- A) NOR

- B) NAND

- C) les 2 dernières réponses

- D) XOR

- E) aucune des 4 dernières réponses

#### 7. Qu'est-ce qu'un "maxterms" ?

- A) une somme de produits logiques

- B) quelque chose que l'expression suivante illustre:  $\bar{a} \cdot b + a \cdot \bar{b}$

- C) une fonction prenant le maximum des termes d'une expression

- D) les 3 dernières réponses

- E) aucune des 4 dernières réponses

#### 8. Quelle formule algébrique résume la table de Karnaugh suivante ?

- A)  $Z = a + \bar{b}$

- B)  $Z = \bar{b} + \bar{d}$

- C)  $Z = \bar{a} \cdot \bar{d}$

- D)  $Z = \bar{b} \cdot \bar{d}$

- E) aucune des 4 dernières réponses

**9. Dans un démultiplexeur à N variables de contrôle, les sorties correspondent aux ... ?**

- A)  $2^N$  minterms des N variables de contrôle

- B)  $2^N$  maxterms des N variables de contrôle

- C)  $2^N$  maxterms des N variables de contrôle

- D)  $2^N$  maxterms des N lignes d'entrée

- E) aucune des 4 dernières réponses

**10. Dans un multiplexeur à 2 variables de contrôle a et b, au moins une des sorties correspond à ... ?**

- A)  $a \cdot b$

- B)  $a \cdot \bar{b}$

- C)  $\bar{a} \cdot b$

- D) les 3 dernières

- E) aucune des 4

**11. Si un décodeur à N entrées dont toutes sont à 1, combien a t-il de sorties à 1 ?**

- A) 1

- B) n

- C)  $2 * N$

- D)  $2^N$

- E) aucune des 4 dernières réponses

**12. Dans une fonction de transfert ...**

- A) la sortie S à l'instant t dépend de l'entrée et de l'état à l'instant t

- B) l'état Q à l'instant t dépend de l'entrée et de l'état à l'instant t

- C) l'état Q à l'instant t dépend de l'entrée à l'instant t

- D) les 3 dernières réponses

- E) aucune des 4 dernières réponses

**13. Dans certaines bascules "synchrone sur front" ?**

- A) la sortie peut changer lorsque le signal d'horloge passe de 0 à 1

- B) la sortie peut changer lorsque le signal d'horloge passe de 1 à 0

- C) les 2 dernières réponses

- D) la sortie change lorsque que le signal d'horloge a atteint 1 ou 0

- E) aucune des 4 dernières réponses

**14. Pour une bascule T avec une entrée t, un état q et une sortie q+, on a ...**

- A)  $q+ = t \cdot \text{non}(q) + \text{non}(t) \cdot q$

- B)  $q+ = \text{non}(t \cdot q) + \text{non}(t + q)$

- C)  $q+ = \text{non}(t \cdot q) + t \cdot \text{non}(q)$

- D)  $q+ = \text{non}(t) \cdot \text{non}(q) + t \cdot q$

- E) aucune des 4 dernières réponses